UNLV Theses, Dissertations, Professional Papers, and Capstones

5-1-2014

# Co-Emulation of Scan-Chain Based Designs Utilizing SCE-MI Infrastructure

Bill Jason Pidlaoan Tomas University of Nevada, Las Vegas

Follow this and additional works at: https://digitalscholarship.unlv.edu/thesesdissertations

Part of the Computer Engineering Commons, Computer Sciences Commons, and the Electrical and Computer Engineering Commons

#### **Repository Citation**

Tomas, Bill Jason Pidlaoan, "Co-Emulation of Scan-Chain Based Designs Utilizing SCE-MI Infrastructure" (2014). *UNLV Theses, Dissertations, Professional Papers, and Capstones*. 2152. http://dx.doi.org/10.34917/5836171

This Thesis is protected by copyright and/or related rights. It has been brought to you by Digital Scholarship@UNLV with permission from the rights-holder(s). You are free to use this Thesis in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you need to obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/or on the work itself.

This Thesis has been accepted for inclusion in UNLV Theses, Dissertations, Professional Papers, and Capstones by an authorized administrator of Digital Scholarship@UNLV. For more information, please contact digitalscholarship@unlv.edu.

## CO-EMULATION OF SCAN-CHAIN BASED DESIGNS UTILIZING SCE-MI INFRASTRUCTURE

By:

Bill Jason Pidlaoan Tomas

Bachelor's Degree of Electrical Engineering

Auburn University 2011

A thesis submitted in partial fulfillment of the requirements for the

Masters of Science in Engineering – Electrical Engineering

Department of Electrical and Computer Engineering

Howard R. Hughes College of Engineering

The Graduate College

University of Nevada, Las Vegas May 2014

#### THE GRADUATE COLLEGE

We recommend the thesis prepared under our supervision by

#### **Bill Jason Pidlaoan Tomas**

entitled

## Co-Emulation of Scan-Chain Based Designed Utilizing SCE-MI Infrastructure

is approved in partial fulfillment of the requirements for the degree of

# **Master of Science in Electrical Engineering Department of Electrical and Computer Engineering**

Yingtao Jiang, Ph.D., Committee Chair

Mei Yang, Ph.D., Committee Member

Henry Selvaraj, Ph.D., Committee Member

Evangelos Yfantis, Ph.D., Graduate College Representative

Kathryn Hausbeck Korgan, Ph.D., Interim Dean of the Graduate College

**May 2014**

#### **Abstract**

Simulation times of complex System-on-Chips (SoC) have grown exponentially as designs reach the multi-million ASIC gate range. Verification teams have adopted emulation as a prominent methodology, incorporating high-level testbenches and FPGA/ASIC hardware for system-level testing (SLT). In addition to SLT, emulation enables software teams to incorporate software applications with cycle-accurate hardware early on in the design cycle. The Standard for Co-Emulation Modeling Interface (SCE-MI) developed by the Accelera Initiative, is a widely used communication protocol for emulation which has been accepted by major electronic design automation (EDA) companies.

Scan-chain is a design-for-test (DFT) methodology used for testing digital circuits. To allow more controllability and observability of the system, design registers are transformed into scan registers, allowing verification teams to shift in test vectors and observe the behavior of combinatorial logic. As SoC complexity increases, thousands of registers can be used in a design, which makes it difficult to implement full-scan testing. More so, as the complexity of the scan algorithm is dependent on the number of design registers, large SoC scan designs can no longer be verified in RTL simulation unless portioned into smaller sub-blocks. To complete a full scan cycle in RTL simulation for large system-level designs, it may take hours, days, or even weeks depending on the complexity of the circuit.

This thesis proposes a methodology to decrease scan-chain verification time utilizing SCE-MI protocol and an FPGA-based emulation platform. A high-level (SystemC) testbench and FPGA synthesizable hardware transactor models are developed for the ISCAS89 S400 benchmark circuit for high-speed communication between the CPU workstation and FPGA emulator. The emulation results are compared to other verification methodologies, and found to be 82% faster than regular RTL simulation. In addition, the emulation runs in the MHz speed

range, allowing the incorporation of software applications, drivers, and operating systems, as opposed to the Hz range in RTL simulation.

#### **Acknowledgements**

The work of this thesis owes the utmost of gratitude to those who contributed to my academic, professional, and personal growth. Compiled over span of three and a half years, my thesis has been a collection of industrial experience in the electronic and design automation (EDA) industry, and a strong foundation of the electrical engineering field set by my professors.

I would like thank my graduate advisor and professor/s, Dr. Yingtao Jiang and Dr. Mei Yang, for instilling the fundamental theorems, ideas, and principles for verifying digital designs using field programmable gate arrays (FPGAs). Through a mixture of challenging semester-long projects and hands-on lab experiments, Dr. Jiang and Dr. Yang ensured my readiness to enter the industry with experience utilizing the latest tools used by design verification engineers and system-on-chip designers. Dr. Jiang has also mentored me throughout my entire experience as a graduate student. He has allowed me to maintain my coursework, providing me flexibility in balancing the workload between being a student and a verification engineer.

For the duration of my time as a hardware emulation product engineer, I would like to thank Kryzstof Szcur and Zbigniew Zalewski of Aldec, Inc. Krysztof and Zibi provided me the opportunity to learn the basics of FPGA-based emulation systems, often begin patient with me through numerous questions and run-time errors. Together, they both understood that young engineers brought new ideas to the table when solving existing problems in the emulation industry. Coupled with guidance in teaching the Standards Co-Emulation Modeling Interface (SCE-MI), my experience at with Krysztof and Zibi at Aldec allowed me to build on my verification experience by utilizing the latest in technology and standards.

While studying for my bachelor's degree in computer engineering at Auburn University, I would like to give much appreciation and gratitude to Dr. Charles Stroud. Dr. Stroud provided me the opportunity to learn more about reconfigurable logic, placing me on his undergraduate research team working on fault simulation of embedded multiplier built-in-self-test (BIST). With his extensive background working at Bell Labs, Dr. Stroud taught me everything he knew about FPGAs, and undoubtedly, is the main reason why I chose digital hardware design and verification as my main focus in my career.

Lastly, I would like to thank my family and friends for keeping me focused on reaching my goals, all the while maintaining a sense of humility. The life lessons learned in being both a student and practicing engineer at times were overwhelming, but thanks to my family and friends, the weight on my shoulders always seemed manageable.

### **Table of Contents**

| Abstract                                                          | iii |

|-------------------------------------------------------------------|-----|

| Acknowledgements                                                  | iv  |

| List of Tables                                                    | ix  |

| List of Figures                                                   | x   |

| Introduction                                                      | 1   |

| Scan Chain Scalability                                            | 2   |

| Scan Insertion                                                    | 3   |

| Abstraction Level of Verification                                 | 5   |

| Event-Based RTL Simulation Bottleneck                             | 7   |

| HW/SW Development Platforms & Debug                               | 10  |

| Standard Co-Emulation Modeling Interface (SCE-MI) <sup>[19]</sup> | 16  |

| Usage                                                             | 17  |

| Macro-based message passing interface                             | 17  |

| Untimed Software Level                                            | 18  |

| Cycle-accurate Hardware Level                                     | 19  |

| Transactions                                                      | 20  |

| Controlled and Uncontrolled Time                                  | 21  |

| Methodology Test Plan                                             | 22  |

| Design Under Test – ISCAS S400 Benchmark                          | 22  |

| Test Bench & Plan                                                 | 24  |

| RTL Simulation & Profiling                                        | 26  |

| Simulation Acceleration                                           | 27  |

| Transaction-Based Emulation                                       | 31  |

| Modified Transaction-Based Emulation                              | 39  |

| FPGA-based Emulator [22]                                          | 41  |

| Results & Analysis                                                | 42  |

| RTL Simulation Results                                            | 42  |

| Simulation Acceleration Results                                   | 46  |

| Transaction-Based Emulation Results                               | 49  |

| Pass-Through Transactor | 49 |

|-------------------------|----|

| FSM Transactor          | 54 |

| Complexity Analysis     |    |

| Resource Analysis       |    |

| Future Work             |    |

| Conclusion              | 63 |

| Bibliography            |    |

| CV                      |    |

## **List of Tables**

| Table 1: Xilinx FPGA Device Properties                              | 3  |

|---------------------------------------------------------------------|----|

| Table 2: Synthesizable vs. Non-Synthesizable Logic                  | 28 |

| Table 3: Test Sequences                                             | 33 |

| Table 4: RTL Simulation Results                                     | 45 |

| Table 5: RTL Profiler Results                                       | 46 |

| Table 6: Simulation Acceleration Synthesizable Logic                | 48 |

| Table 7: Synthesizable Logic with Debug Resources                   | 48 |

| Table 8: Simulation Acceleration Results                            | 49 |

| Table 9: Estimated vs. Measured Simulation Acceleration Speedup     | 49 |

| Table 10: SCE-MI Pass Through Synthesizable Logic                   | 50 |

| Table 11: SCE-MI Pass Through Synthesizable Logic Debug Resources   | 51 |

| Table 12: SCE-MI Pass Through Transactor Results                    | 53 |

| Table 13: Pass Through Transactor Emulation Comparison              | 54 |

| Table 14: SCE-MI FSM Transactor Synthesizable Logic                 | 55 |

| Table 15: SCE-MI FSM Transactor Synthesizable Logic Debug Resources | 55 |

| Table 16: SCE-MI FSM Transactor Results                             | 56 |

| Table 17: SCE-MI Emulation Comparisons                              | 56 |

| Table 18: RTL Simulation Clock Cycle Workload                       | 57 |

| Table 19: SCE-MI Controlled Clock Cycle Results                     | 58 |

## **List of Figures**

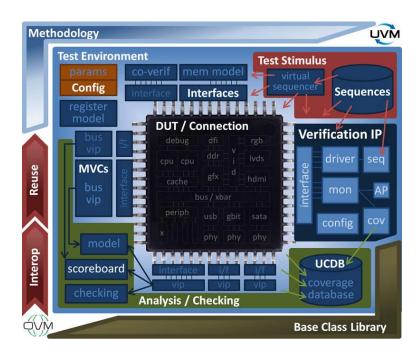

| Figure 1: UVM-based Test Environment.                                       | 6  |

|-----------------------------------------------------------------------------|----|

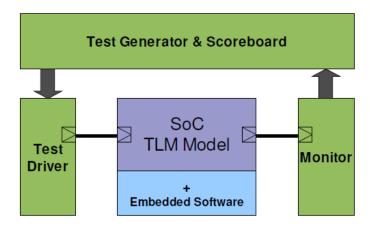

| Figure 2: TLM-based Test Environment                                        | 7  |

| Figure 3: Scan Chain Event-based Simulation                                 | 9  |

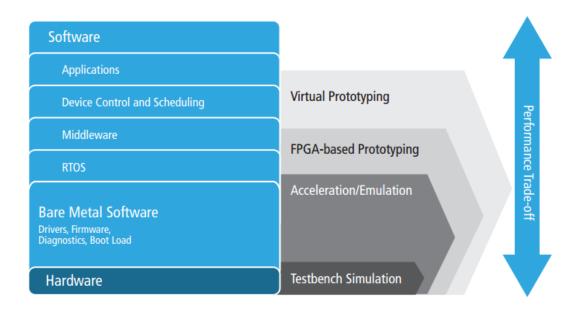

| Figure 4: Verification Techniques for Different Levels of Logic             | 10 |

| Figure 5: Aldec FPGA-based Prototyping Platform HES-7                       | 12 |

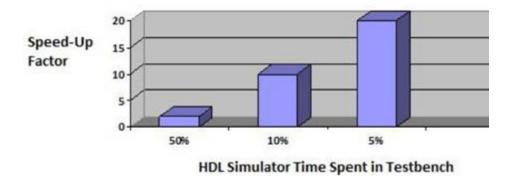

| Figure 6: Speed-up vs. HDL Testbench Time                                   | 14 |

| Figure 7: SCE-MI Infrastructure                                             | 18 |

| Figure 8: Untimed Testbench Models Connected to DUT                         | 19 |

| Figure 9: SCE-MI Abstraction Bridge                                         | 20 |

| Figure 10: SCE-MI Clocking                                                  | 22 |

| Figure 11: DFF Scan Conversion                                              | 23 |

| Figure 12: Top-Level DUT with Scan FFs Instantiated                         | 24 |

| Figure 13: Testbench Reset Assertion                                        |    |

| Figure 14: S400 Scan Chain Test Sequence                                    | 26 |

| Figure 15: RTL Simulation Test Environment                                  | 27 |

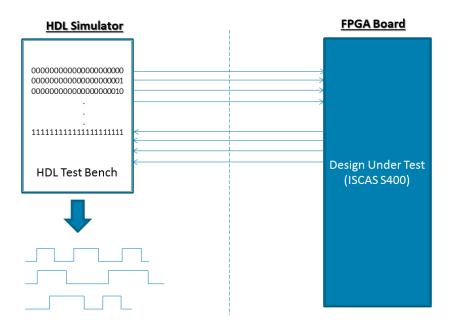

| Figure 16: Simulation Acceleration Test Enviornment                         | 29 |

| Figure 17: Splitting RTL Simulation Environment for Simulation Acceleration | 30 |

| Figure 18: Emulation Setup Flow                                             | 31 |

| Figure 19: Testbench Scan Sequence                                          | 34 |

| Figure 20: Transactor Pass Through Assignments                              | 35 |

| Figure 21: SCE-MI Message In-Port                                           | 36 |

| Figure 22: SCE-MI Message In-Port Software Implementation                   | 37 |

| Figure 23: SCE-MI Pass Through Test Environment                             | 39 |

| Figure 24: SCE-MI FSM Test Environment                                      | 40 |

| Figure 25: Transactor FSM Transitions                                       | 41 |

| Figure 26: Aldec HES-5 Prototyping Board                                    | 42 |

| Figure 27: TCL Timer Processes                                              | 44 |

| Figure 28: Simulation Acceleration Emulation Setup                          | 47 |

| Figure 29: SCE-MI Generated XML                                             | 52 |

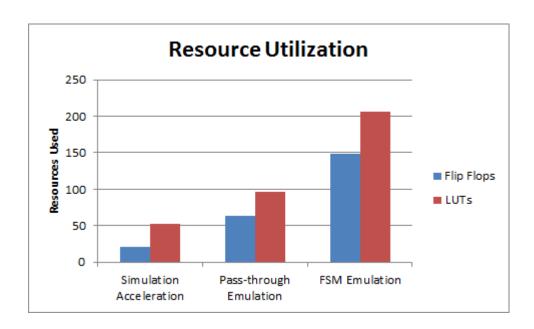

| Figure 30: Resource Utilization for Acceleration and Emulation              | 59 |

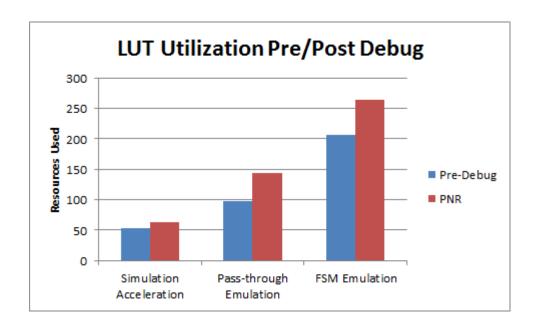

| Figure 31: LUT Utilization Pre/Post Debug Implementation                    |    |

#### Introduction

Integrated circuitry on a grand scale is prevalent in everyday human interaction. These systems range in complexity from small motor control circuits to large mobile phone system-on-chips (SoC). As technological processes continue to advance, customers are demanding smaller, faster, and higher throughput devices. Engineers developing these very large scale integrated (VLSI) devices, are faced with the challenges of verifying systems which can consists of millions of gates, mixed-signal (digital and analog) implementations, and new physical characteristics.

To gain controllability and observability into a digital system, designers utilize the 'Scan-Chain' testing methodology. This methodology transforms a register to a scan register (sometimes referred to as a scan flip-flop), by adding a multiplexer circuit at the input of the register, and a control signal which enables the designer to select between the primary IO and scan IO [1]. These registers are then serially connected to one another creating a scan chain. With the scan-chain signals tied to device IO, designers and verification engineers can serially input a test sequence, and observe the resulting output.

The overall goal of this thesis is to address the issues of scan chain implementation in large scale SoC devices, and provide a solution which can be quickly integrated into the traditional digital design and verification flow. In the proceeding section, we observe problems regarding scan chain scalability when working with multi-million gate system designs. The next section will cover issues dealing with inserting scan logic into the design at the register transfer level (RTL). We will also discuss how the abstraction level of digital design verification is being elevated toward a software-based approach utilizing high-level models. This approach when coupled with scan chain presents new issues, since hardware developers and software engineers co-exist on the same platform. Next, the introduction will cover the bottleneck that event-based

RTL simulators when simulating scan chain designs. The section will conclude with covering HW/SW development platforms, in which scan chain designs can be run and debugged.

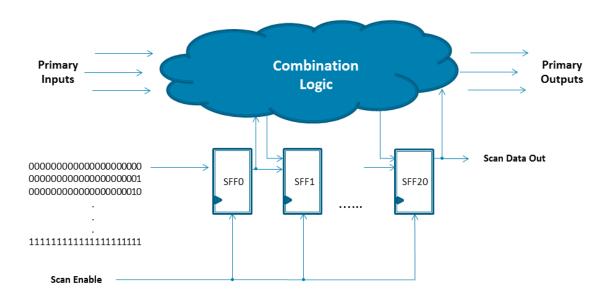

#### **Scan Chain Scalability**

Test methodologies have encountered many issues when dealing with large scale SoC designs, simply due to the magnitude and complexity of the SoC. Complete systems now encompass multiple blocks ranging from mixed-signal modules, embedded processors, 3<sup>rd</sup> party intellectual property (IP), and more. Gate count of these systems can quickly grow as all these modules are put together to form a complete SoC device. Today, an average mobile SoC device is greater than 4M ASIC gates, and can utilize thousands of registers [2]. For scan chain designs, the increase in register count is directly dependent on the complexity of the full scan algorithm and test time [3]. The complexity for full scan method can be calculated as follow:

- 1. A test vector takes 'n' clock cycles to be completely shifted in serially to the scan chain and assert to the combinatorial logic (n+1).

- 2. The total number of possible combinations for an 'n' register scan chain is **2**<sup>n</sup> since each register can exercise a 0 or 1 state.

- 3. The last test vector takes 'n' clock cycles to be completely shifted out serially from the scan chain.

Full Scan Complexity =

$$[(Scan In + assert)(2^n)] + n = 2n(2^n - 1)$$

=  $O[n + 1(2^n)] + n$

Scan chain implementation transforms a single register to a scan register by implementing switch logic at the input. This transform causes an additional area penalty to the circuit, since every register in the design has to undergo the scan transformation. FPGA systems, platforms commonly used to verify digital designs, are limited by the number of look-up-tables

(LUTs) and flip flops available on the device. Although LUT count has steadily increased in FPGA devices, as shown in table 1 below for Xilinx FPGAs[3] [4] [5], SoC designs are advancing at a faster pace than their technological counterpart.

|                     | Virtex-5     | Virtex-6    | Virtex-7    |

|---------------------|--------------|-------------|-------------|

|                     | (XC5VLX330T) | (XC6VLX760) | (XC7V2000T) |

| Slices              | 51,840       | 118,560     | 305,400     |

| LUT Count           | 207,360      | 474,240     | 1,221,600   |

| Max Distributed RAM | 3420         | 8,280       | 21,550      |

| (Kb)                |              |             |             |

**Table 1: Xilinx FPGA Device Properties**

There exist variant scan methodologies, such as partial-scan, in which only a subset of all registers are transformed into a scan-chain mitigating the area penalty. This variance decreases the test time and area penalty, but also decreases the effectiveness of the test since all registers and logic are not tested [7]. For the remainder of this thesis, the scan methodology which will be used is the full-scan implementation, which utilizes all registers in the design. In addition to full scan, this thesis will utilize complete test vector set, meaning all possible combinations are exercised at the scan input. Test compression and automatic test pattern generation (ATPG) methodologies used to reduce the number of vectors to attain a certain fault coverage (FC%), are not used in this thesis.

#### **Scan Insertion**

Hardware designs typically begin with a user specifications outlining required IO, system functionality, and expected output. Designer engineers utilize hardware description languages (HDL) to characterize the system on the RTL level, to be able to observe signal data between synchronous elements. Verification engineers, often working concurrently with design engineers, develop testbenches which are used to verify that the circuit is functioning as expected.

Testbenches can vary in complexity from simple reset sequences, to comparing packet transfers between a master and slave device. For scan chain insertion, users have two choices to transform design RTL code:

- 1. Manually manipulate the RTL This includes coding the scan registers at the RTL level, and adding them to a design hierarchy. This of course it not accomplished on the system level since it requires scan registers to be added to every block of the design. The top level only serves to instantiate connections between the modules, or in this focus, connect scan registers from one block to another The system level testbench will also require modification, since the system must be tested with the inserted scan chain. This includes toggling between test data from the user, and normal system functionality. Manually manipulating the RTL incurs a large time penalty, since it requires extra coding and verification, but does not require the extra cost in software test tools.

- 2. **EDA Design-for-Test (DFT) Insertion [8]** EDA vendors tool typically transform RTL code into a single synthesized netlist. This netlist maps RTL code to gate-level primitives for ASIC devices, or FPGA primitives for FPGA devices. For the latter, primitives are stored in FPGA libraries specific for each FPGA vendor. EDA tools input these FPGA libraries, and transform your design using primitives for the targeted device. For scan insertion, the user generally specifies test signals to be used in the design. The DFT-insertion tool generally has its own libraries used for scan insertion, which modify the primitives used by the FPGA vendor. This way they can manipulate the netlist by adding scan logic to existing register primitives. Most software tools also contain scan compression algorithms and built-in fault simulators, which can generate automatic testbenches for the scan inserted design. Although this

allows for faster bring-up of the design, DFT-insertion tools can be quite expensive. For projects with a restricted budget, extra test software/hardware may not be feasible.

The difficulty in using scan test for large SoC designs, is balancing the verification of scan logic and test time. Companies with large design teams have dedicated bandwidth for DFT-implementation or have access to software tools. Most of the project time is consumed by verification engineers, since every mode and functionality of the circuit must be exercised in the testbench [9]. From the previous section, we can see that the complexity of the scan algorithm exponentially increases as the number of registers in the design increases. Since the testbench HDL has to be modified to observe data signals from the scan registers, this incurs a longer verification cycle if a large amount of registers are used.

#### **Abstraction Level of Verification**

When designing systems on the block level, hardware designers create testbenches specific to that blocks functionality. When block level specifications are finished, verification teams validate the top level, or system functionality. Tests on the system level are more complex than the block level, since the system usually has to communicate with outside interfaces which transmit real-time data. For example, when developing a router, the DUT has to interface with a host workstation via Ethernet to observe packet transfers. To tackle the complexity of validating at the system-level, verification engineers typically utilize higher levels of abstraction with hardware verification languages (HVL). HVL's such as SystemVerilog, SystemC, C, and C++ contain libraries which contain sequencers, scoreboards, code coverage, and many other tools which aid in the verification process. Figure 1 showcases a test environment based of the universal verification methodology (UVM), a verification extension of the SystemVerilog language [10].

Figure 1: UVM-based Test Environment

Since higher levels of abstraction are being used to validate SoC designs, they should also incorporate test environments aimed specifically for scan design. Classes and functions utilizing HVLs can be created to automatically handle each step in the scan process. This allows for different possibilities in handling scan data such as: dumping data to text files, comparing output vectors against a golden set, and utilizing software constructs for scan automation. This however poses a challenge since design and verification engineers use different languages in accomplishing their goals.

Design engineers utilize low-level of abstraction with Verilog and VHDL, while verification engineers mainly commonly SystemVerilog, SystemC, C, and C++. While there has been a push for integration between HVLs and HDLs, typically engineering teams use this structure. For example, SystemC is an event-drive interface between high-level C++ and RTL, which provide SW engineers an environment to simulate hardware models [11]. These models, called transaction level modeling (TLM) blocks are written in C++ and can be simulated and connected to HW RTL models through a programming language interface (PLI). Moreover,

software engineers can utilize these high level HW models into an environment to test against while developing software drivers, applications, and operating systems [12]. Figure 2 showcases a complete verification environment encompassing TLM models with verification constructs available in HVLs.

Figure 2: TLM-based Test Environment

For scan based design in today SoC, a verification methodology must be developed which integrates high level verification, with low level functionality. These two environments and teams should be separated when establishing scan RTL and verification plans for the scan chain, but must utilize a standard process which encapsulates both into a single validation cycle. This will allow the verification team to develop test plans and TLM models with high levels of abstraction for HW/SW integration, while allowing HW engineers to reuse pre-existing RTL testbenches.

#### **Event-Based RTL Simulation Bottleneck**

The previous sections outlined various issues dealing with algorithm complexity and RTL issues when adding scan registers to large scale SoC systems. This section will discuss issues during verification of scan chain systems using RTL simulators. RTL simulation test time is dictated by the complexity of the test bench and the design, and the workstation CPU. Another factor is the RTL simulation tool used by the verification team. There are two types of RTL

simulators used for verification: event-based and cycle-based. Since the simulator we will be using (Aldec Riviera-PRO) in this thesis will be event-based, we will focus on its specific bottleneck.

An event-based simulator updates whenever an event occurs, be it combinatorial or sequential [13]. Event-based simulators can capture transitions through a combinatorial datapath, which may not be aligned with a clock edge allowing users to capture issues such as glitches. Events are placed in a timing queue, which is evaluated in the order the events are placed [14]. In terms of CPU usage, a majority of the workload is utilized to update the events queue. For a design with a large number of events, the design queue will be constantly updated, leading to large simulation times.

For scan chain verification, there exist a large number of events, since data must pass through both sequential and combinational paths in a single clock cycle. Figure 3 shows cases a scan chain operation, and how an event-based simulator would fill the timing queue. First is to assert test mode through all switch logic on the scan registers. Since all events are captured, the transition from normal mode to test mode is placed in the events queue for all scan registers. After inputting data the TDI pin, a clock is applied, and the state of each register changes. The clock transitions and register states changing are all added to the timing queue. After applying the complete vector into the chain, the test mode is de-asserted, and all switch logic must be transitioned back to normal mode. As previous, all state changes to the switch logic is then added to the queue. After a clock cycle is applied, register data must pass through combinational logic in which the numbers of events added are dependent on logic level/gates. If there is a large amount of combination logic between registers, than the events queue can grow quickly since there exists combination paths between all 'n' number of registers.

| Scan Chain Operation                         | Event-based Simulation                           |

|----------------------------------------------|--------------------------------------------------|

|                                              | Queue                                            |

| Assert test mode                             | Assert test mode                                 |

| Input TDI (single bit)                       | Scan register 0 MUX switches to test mode        |

|                                              |                                                  |

|                                              | Scan register 'n' MUX switches to test mode      |

| Apply clock                                  | Input TDI (single bit)                           |

| Repeat for 'N' number of registers and clock | Apply clock                                      |

| cycles until complete vector is shifted-in   |                                                  |

| De-assert test mode                          | Repeat for 'N' number of registers and clock     |

|                                              | cycles until complete vector is shifted-in       |

| Apply clock                                  | De-assert test mode                              |

| Output TDO (single bit)                      | Scan register 0 MUX switches to normal mode      |

|                                              |                                                  |

|                                              | Scan register 'n' MUX switches to normal mode    |

| Repeat for $2^n$ possible combinations       | Apply Clock                                      |

|                                              | Data signal changes through combinatorial path 0 |

|                                              |                                                  |

|                                              |                                                  |

|                                              | Data signal changes through combination path n   |

|                                              | Output TDO (single bit)                          |

|                                              | Repeat for 2 <sup>n</sup> possible combinations  |

Figure 3: Scan Chain Event-based Simulation

As seen how above, depending on the number of registers, and the combinatorial path between those registers, the event queue can grow very large. Since large SoC designs can contain thousands of registers, simulation time can take hours or even days depending on the system complexity. Also, a bulk of the transitions occurs between the combinatorial paths between all scan registers. To speed up this process, we need to utilize a development platform which will allow us to place the scan chain into hardware and remove it from the simulation environment.

#### **HW/SW Development Platforms & Debug**

In the previous sections, I discussed the challenges in verifying scan based designs such as: scan insertion, high level of abstraction with HVLs, and increased algorithm complexity when dealing with a large number of scan registers. This section will address issues and use cases when utilizing different development platforms for scan testing. Each platform has advantages and disadvantages in terms of: speed, cost, debug capabilities, and bring-up. Figure 4 showcases the various platforms with the different HW/SW levels which is applicable for verification [15].

Figure 4: Verification Techniques for Different Levels of Logic

For each platform, we will discuss use cases and how scan chain verification can be accomplished. The four main HW/SW development platforms for SoC designs are:

- 1. **Testbench (RTL) Simulation** This is the main way of verifying design blocks utilizing Verilog, VHDL, or SystemVerilog. Besides utilizing language specific constructs such as monitors, random sequence generators, waveform dumps, etc., verification methodologies such as UVM or OVM have made the verification process more complete. For scan testing, a user can simply initialize test vectors established from fault simulation into a text file, and use HDL constructs to feed the data serially into the scan data input. In similar fashion, data from the scan out can be outputted to a text file to be analyzed at a later time or compared to against a golden set. The biggest advantage of using RTL simulation is that all signal transitions are presented to the user through waveform viewers, schematic editors, and various debug tools available for each EDA vendor. If there is an incorrect value in the scan out output, user can observe all signals in the chain as well as the current state all scan registers. This allows the user to quickly debug a broken scan chain. Although this is the lowest cost of all platforms, we see from the previous sections that large SoC designs incur very long simulation cycles. In this manner, a scan chain cannot quickly be verified on the system level because bugs can only be found at the end of the simulation run.

- 2. FPGA-based Prototyping Prototyping platforms, such as the Aldec HES-7 show in Figure 5 below, utilize FPGA place and route process with a generated bitstream which is implemented onto FPGA memory [16]. RTL is synthesized and mapped to FPGA primitives, which then runs through a placer which connects the primitives with FPGA interconnect. All data being passed through the FPGA place and route (PNR) process must be synthesizable, meaning the code must be able to be mapped onto FPGA

primitives. This does not include typical testbench constructs such: delays, initial values, or system functions.

Figure 5: Aldec FPGA-based Prototyping Platform HES-7

Most prototyping boards include peripherals and connectors, (PCIe, RS232, USB,) which the user can map design IO to a target device. Since the entire design is running in hardware, it is capable of running at faster clock frequency than RTL simulation. The disadvantage of using an FPGA-based prototype is there is little debug capabilities since signals cannot be observed using a waveform viewer [16]. On-board logic analyzers such as Xilinx ChipScope Pro and Altera SignalTap, mitigate the issue, but with a limited number of bits to be sampled, they do not provide a complete debug environment. Debugging a scan chain is difficult when implemented onto an FPGA, since users can only observe the scan in and scan out data. If a scan register contains an incorrect value, it must propagate through the entire chain before being observed at the output.

- 3. Acceleration/Emulation Acceleration and emulation platforms combine the debugging environment from RTL simulation with the speed of an FPGA prototype. In these systems, a workstation with an RTL simulator directly connects to a FPGA prototype via high-speed interfaces (Ethernet, PCIe). Emulation teams develop hardware drivers for the physical interface and a software library to establish communication between the hardware and software. From this point, users can utilize two different modes of operation:

- a. Simulation Acceleration [16] With this mode, synthesizable constructs are implemented onto the FPGA hardware, while non-synthesizable (Testbench) constructs remain in the RTL simulator. Simulation acceleration is a signal-based interface, as data is passed serially through the high speed channel. This mode is faster than RTL simulation, if the majority of the simulation time is not spent inside the testbench. If the testbench contains a majority of the simulation time, than the emulator will spend a most of the time in the communication structure between the hardware and software. Most simulators have a profiler tool which allows the user to locate this module requires the largest amount of CPU usage and simulation time. With this information, the amount of speedup can be determined prior to running acceleration. In Figure 6 below, a table is show with the amount of speed up a design can attain depending on the time spend in the test bench.

Figure 6: Speed-up vs. HDL Testbench Time

Modifying the test environment to have a majority being placed in the FPGA, allows for the fastest simulation acceleration run. In addition to the speed, the software library directly connects to an RTL simulator, allowing verification teams to observe signals implemented on HW. For scan design, the testbench will serially shift in/out data to the scan chain, leading to constant communication between hardware and software. If the test environment is not modified, the user will not be able to achieve fast simulation times.

b. Transaction-based Emulation [17] – In transaction-based emulation, the communication channel utilizes transactions, as opposed to signals in simulation acceleration. This is accomplished with high level testbenches on the software side, and bus functional models (BFMs) which translate high level messages to low level signals which are input to the DUT. The translators are commonly referred to as transactors, and typically implemented as finite state machines (FSMs), which send many signals to the DUT based on a single message. In this manner, a single message from the high level test bench, can equate to hundreds of clock cycles in hardware, and conversely hundreds of clock cycles in hardware, can equate to a single message when sent to the software. The

Accelera Systems Initiative, the creators of SystemC, developed the standard coemulation modeling interface (SCEMI), which defines a model for simulations to

run in an emulation environment and vice versa. SCE-MI defines the

communication between transactor/ message port models running in hardware

(clock edges) and high-level testbenches (C/C++ processing). Debug can be

accomplished in the RTL simulator, since the hardware encompasses the

transactor and DUT within the FPGA. Signals sent from the software side

(through the transactor) and the scan chain can be observed on the waveform

viewer, allowing users to debug broken scan chains which have incorrect values.

Since SCE-MI standards define all system clock operations (which includes the

capability to 'freeze' the clock) – users do have to worry about how clocking and

reset synchronization occurs.

4. Virtual Prototyping [18] – Virtual platforms allow software engineers to model system-level behavior using TLM models. These high-level models can be paired with the development of a software stack, which can model the behavior of a system at real-time speeds. Today's virtual platform systems have a large portfolio of operating systems, peripherals, processors, bus models, and various blocks which are commonly found in SoC devices. Software engineers can utilize the TLM models for customer demos which can present an early reference model prior to hardware development. The disadvantage of using a virtual prototype is that they are not a good representation of cycle accurate hardware behavior. In hardware, data signals transition based on clock edges, while TLM models are processed serially line by line similar to a C/C++ program. Although SystemC models have improved since being developed in 1999 to model hardware closely, it cannot be directly translated to FPGA or ASIC gate primitives as easily as RTL. For scan design, the virtual prototypes utilize high level models, so a high-level

model for a serial communication device (ex. JTAG) can be directly connected to the scan chain. Engineers can utilize C/C++ debugging tools such as the GNU Debugger (GDB) to observe the software stack while signals transition in and out of the scan chain. Since these are high-level models, and will not be implemented into an FPGA, they are only representative of the hardware functionality, and not its implementation behavior.

Depending on which platform is used for hardware and software development, the debugging capabilities for verifying scan chain implementation differs. The best option would be to utilize a transaction-based emulation platform, since the scan chain will implemented on hardware, and can be verified utilizing transactions from high-level testbenches. Another option available by some FPGA vendors is an FPGA-based emulation platform, which combines the capabilities of an FPGA-based prototyping board with a transaction-based emulator. With this test environment, virtual models available from virtual prototyping solutions can be directly connected to an emulator workstation via software TLM libraries developed by emulation vendors. With high-level models and verification constructs, the scan chain can be verified utilizing timing accurate behavior made available by hardware.

### Standard Co-Emulation Modeling Interface (SCE-MI)<sup>[19]</sup>

This thesis will utilize the SCE-MI standard, which was developed by Accelera in 2007 for communication between hardware and software in emulation platforms. It is worth to note a description of the protocol, to better understand its basic architecture, and use cases when utilized by verification and design teams. Today, Emulation systems and prototyping platforms have emerged as popular verification tools when dealing with large scale SoC designs. Unfortunately engineers have come to many roadblocks when dealing with such tools such as: no debug capabilities, slow emulation speed, and limited API provided by EDA vendors. The SCE-MI protocol was developed to solve the many issues presented by verification teams which were communication bottleneck between hardware and software.

#### Usage

SCE-MI implements a communication infrastructure which allows messages (transactions) to be passed between high-level software models to the device under test implemented in hardware. Ports are established on both sides of the hardware and software link, and messages are conveyed through the link. Since the software side has no notion of a clock, which is commonly used to control events in hardware, data is processed in a 'un-timed' fashion. The SCE-MI architecture is the bridge between the un-timed messages in software and the 'timed' clock events occurring in hardware.

#### Macro-based message passing interface

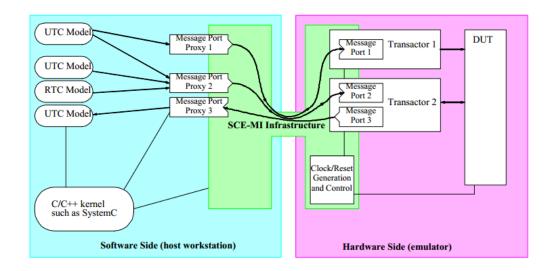

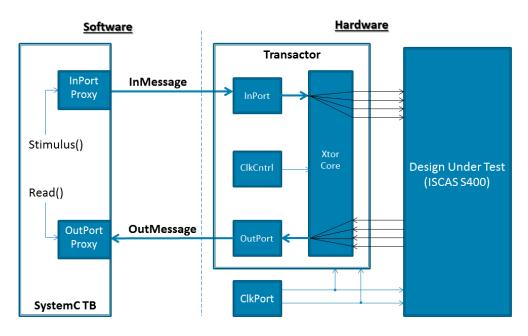

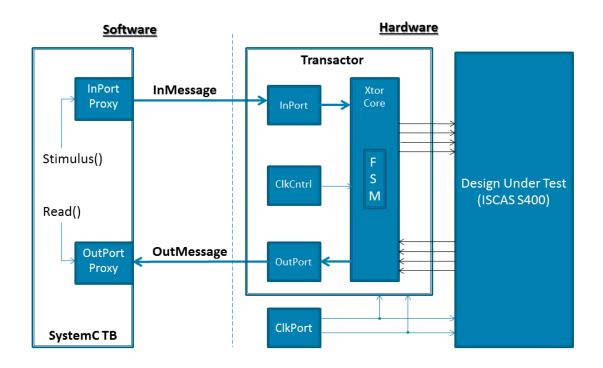

There are three types of SCE-MI interfaces: macro-based, function-based, and pipes-based. For this thesis, we will be using function-based and omit the two latter interfaces. There are 3 main environments when describing the SCE-MI macro-based interface: the hardware side, the software side, and the SCE-MI bridge. On the hardware side, SCE-MI defines a set of synthesizable message ports which relay messages to and from the software side. The transactor is a bus functional model, which translates high level calls from the software side to bit sequences for the DUT. The SCE-MI Infrastructure (shown in Figure 7 below) also contains dedicated clock and reset control logic to be able to control system clocks.

Figure 7: SCE-MI Infrastructure

The software side on the host workstation contains a set of message port proxies, which are implemented as C++ objects which allow the SCE-MI API to access the channel. From the connection to the channel, the proxy can connect to any untimed C model (UTC). The SCE-MI bridge utilizes a dual –ready handshake, in which software proxies and hardware message ports use Receive/Transmit ready signals to inform the other side that it is ready to receive or send data. The bridge channel acts as bi-directional network socket, which carry the message, but it is the responsibility of the transactor to deliver cycle-accurate information to the DUT.

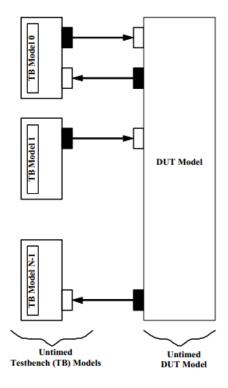

#### **Untimed Software Level**

An untimed environment consists of system level model with a test structure utilizing C/C++ abstract data types (Figure 8 below). These testbench structures can operate a manner similar to RTL testbenches, but can incorporate object oriented programming (OOP) features such as classes, functions, etc. On this level, software engineers can connect the untimed-model to software applications, drivers, or operating systems to send real-time data to the DUT and analyze system-level outputs. Eventually the DUT is prepared with RTL models, which describes the model based on cycle-accurate events. This HDL representation of the DUT will eventually be compiled and synthesized onto a hardware platform. To save time however, the same test

structures which were used in the high-level model can be reused in emulation with low-level RTL models.

Figure 8: Untimed Testbench Models Connected to DUT

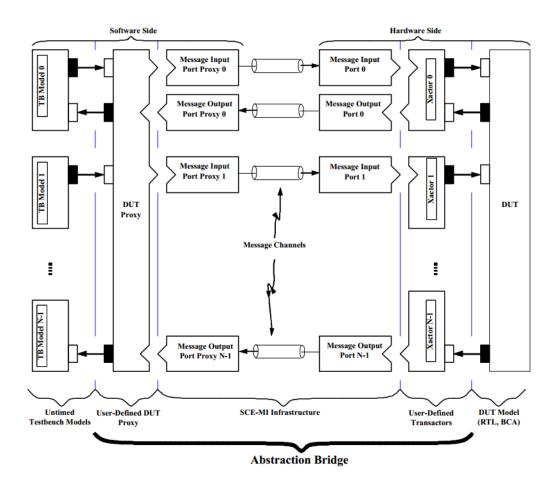

#### **Cycle-accurate Hardware Level**

For a cycle-accurate hardware model, the DUT is implemented based on clocked events which is a more accurate behavior compared to an untimed model on the software side. The SCE-MI infrastructure enacts message ports on hardware, and defines how transaction can be sent to those ports from proxies established on the software side. Along with the message input/output ports are transactors, which translate the high level calls to a sequence of bits which are input stimuli to the DUT. Conversely output data from the DUT is processed in the transactor, and is sent to the software side. The SCE-MI standard guarantees delivery of the untimed message through the transport layer established by the macro-based interface. Figure 9 below, there can multiple instantiations of transactors connected to multiple blocks with a DUT. For example,

multiple high-level testbenches can be testing PCIe, USB, and Ethernet interfaces simultaneously on a SoC DUT, by instantiating multiple transactor cores and software proxy models.

Figure 9: SCE-MI Abstraction Bridge

#### **Transactions**

Transactions beginning on the software side are not constrained to any clocking structure or event as in hardware. With this capability, they can utilize many OOP techniques such as functions, classes, or Boolean vectors when sending data to the hardware. This allows passing messages by value or by reference, but whatever means is chosen, needs to be serialized prior to traveling over the communication channel. It is the job of the proxy to construct the bit vector, based on what is sent from the software model. Another job of the proxy is to analyze bit vectors

traveling from the hardware to the software side, since it needs to be sent to the software model (which can be a class, function, etc.).

The hardware side relies on the transactor core to apply stimulus to the DUT based on the input data delivered from the software side. Based on the data, the transactor applies a sequence of stimulus which relies on clock edges. Output data from the DUT, is processed from the transactor core, which is then sent back to the software side for post-processing and debug. The data which is constructed back to an abstract data type in the software, can span over hundreds of clock cycles in hardware.

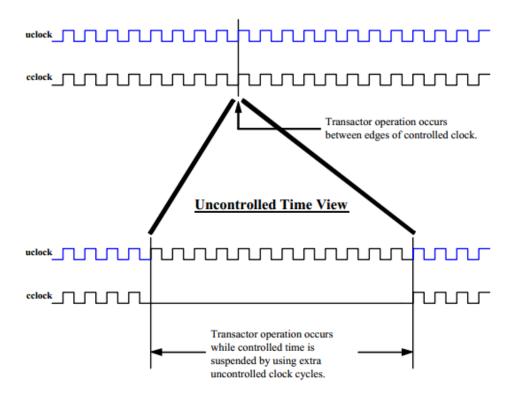

#### **Controlled and Uncontrolled Time**

There exist two different clocks in the SCE-MI infrastructure: uncontrolled clock (Uclock), and controlled clock (Cclock). Uncontrolled clock is the fastest clock available, and is usually provided by an oscillator on an emulator's hardware board. Controlled clock, is the DUT clock which feeds to all the registers in the system design. Data must be able to traverse the abstraction bridge from the software side to hardware, without interrupting the current operation occurring in hardware. When data is sent across the bridge to the message port of a transactor, the controlled clock 'freezes' the Cclock and DUT operation, and enables the transactor operation through the Uclock. Figure 10 displays depicts how frozen cclock would appear on a waveform viewer. Since the top level of the system is running on Uclock, it can be interfaced with operating systems, such as Linux, which require a high speed environment to run applications.

#### Controlled Time View

Figure 10: SCE-MI Clocking

#### **Methodology Test Plan**

#### **Design Under Test – ISCAS S400 Benchmark**

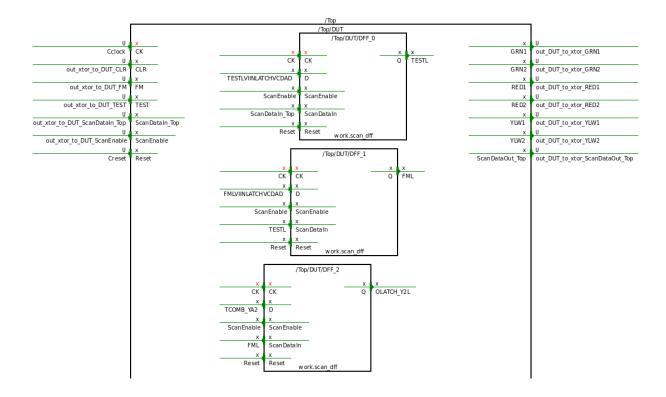

The DUT which will be used for this thesis is the 1989 International Symposium on Circuits and Systems (ISCAS89) S400 sequential benchmark circuit. The S400 is a netlist description of a traffic light controller, which contains 21 registers and 3 primary inputs and 6 primary outputs [20]. The circuit is built with 58 inverters and 106 gates (11 ANDs + 36 NANDs + 25 ORs + 34 NORs). The 400 in the circuit description, represents the number of interconnect lines among the circuit primitives. Amongst the primitives, is a low-level description of a register module built using inverters, tri-states, and NMOS transistors. To modify the benchmark to include scan registers, a scan\_dff module is defined using an RTL description (Figure 11 below).

```

module dff (CK,Q,D);

module scan dff (CK,Q,D,ScanEnable,Sca

input CK,D;

output Q;

//D Flip Flop IO

input CK, Reset, D;

wire NM, NCK;

output Q;

trireg NQ,M;

nmos N7 (M,D,NCK);

//Scan IO

not P3 (NM,M);

input ScanEnable, ScanDataIn;

nmos N9 (NQ,NM,CK);

not P5 (Q,NQ);

//D Flip Flop Reg decleration

not P1 (NCK,CK);

reg Q;

endmodule

always @ (posedge CK)

begin

if (Reset) begin

Q \le 1'b0;

end else begin

if (ScanEnable) begin

Q <= ScanDataIn;

end else begin

Q \leftarrow D;

end

end

end

endmodule

```

Figure 11: DFF Scan Conversion

After the module is defined, all 21 scan registers are daisy-chained to another, with the first input and last output connected to test data in and test data out respectively. In addition, each register will have a reset signal to be able to reset the register to a known state prior to the scan sequence. A 'ScanEnable' signal is also added to each register to be able to put each register into test mode or allow normal functionality when de-asserted. Figure 12 below shows the top level of the DUT with the first 3 scan registers connected to one another. The output of the first scan register (DFF\_0) 'TESTL' is connected directly to the second scan register (DFF\_1) via ScanDataIn. The original signal is connected to the registers data input, and can be toggled with the ScanEnable signal. This daisy chain propagates through all 21 scan flip flops, and the output of DFF\_21 is connected to the signal 'out\_DUT\_to\_xtor\_ScanDataOut\_Top' which feeds back to

the transactor. To verify the functionality of the DUT, a testbench will be generated exercising all possible vector inputs ( $2^{21} = 2097152$ ) and verified using RTL simulation.

Figure 12: Top-Level DUT with Scan FFs Instantiated

#### **Test Bench & Plan**

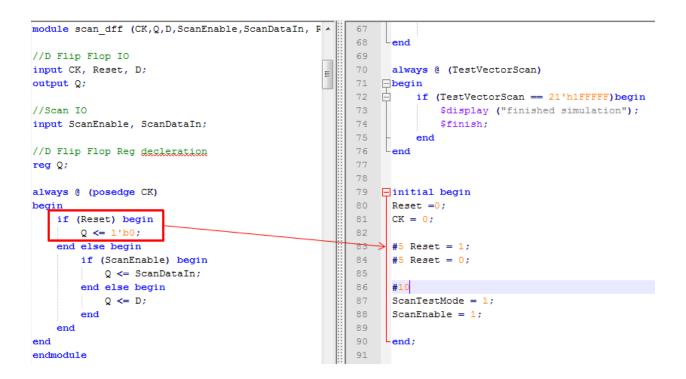

The testbench will verify the functionality of the circuit during RTL simulation. Prior to creating the testbench, a test plan needs to be created to exercise all modes of operation. Since we are primarily focusing on scan chain operation, we will need to create multiple test sequences for the DUT. The four test sequences which will be used are the reset toggle, scan enable toggle, scan sequence, and clock generation.

The first two test sequence puts the DUT into a known state, and enables operation of the scan chain. For the reset toggle in Figure 13, an active-high reset signal initializes all scan registers with a '0' value, allowing the DUT to clear any data which may be held during circuit initialization. During the testbench initialization, the reset is set low and is asserted/de-asserted

prior to the scan enable toggle sequence. The scan enable toggle sequence, allows the testbench to shift in test vectors serially into the test data in port of the first scan register. The scan enable deasserts when the vector is completely shifted into the scan-chain, capturing the output of the combination logical back into the scan chain registers. When the capture is finished, the scan enable is asserted once more, which shifts out the current vector in the chain while simultaneously shifting in the next vector in the test sequence.

Figure 13: Testbench Reset Assertion

The scan sequence serially shifts in test vectors in the DUT when the scan enable toggle sequence is occurring. For the scan sequence, we will exercise full-scan mode, which utilizes all  $2^{21}$  test vectors from all zeroes to all ones (Figure 14). Since the reset toggle sequence sets the registers to all zeroes, we can eliminate the first bit vector, and observe the output of combination logic without the first shift sequence. The next vector (21'd1) is initialized with a counter, which increments after the last vector is completely shifted into the scan chain. The counter is constrained to  $2^{21}$  vectors, and when it reaches the upper-bound, the testbench automatically

exits following the last vector being shifted out. The clock generation, generates the clock pulse, which feeds the scan registers and controls the speed of the DUT. For this simulation we will set the clock speed to 100MHz with a force command in the simulators debug properties. The main focus during RTL simulation is to determine where the testbench is spending a majority of the simulation time in the testbench. Although the clock speed can be adjusted, the CPU will throttle the performance based on current processes occurring, CPU multi-thread capabilities, CPU cores available, etc. Using the simulators profiler tool, we can gather a better understanding of how the CPU handles different portions of the testbench [16].

Figure 14: S400 Scan Chain Test Sequence

## **RTL Simulation & Profiling**

The modified ISCAS S400 netlist will be first simulated with the Aldec Riviera-PRO functional verification platform [21]. Test bench and test sequence will reside in the workstation CPU. RTL simulation serves as the median to verify circuit operation, and allow debugging using the waveform viewer tool. Another feature of Riviera-PRO is the schematic view of the system (Figure 15), which allows users to visualize data transfers between instances in the DUT. The testbench based on the test sequence in the prior section (full-scan) is implemented on a HP

Laptop with an Intel Core Duo CPU clocked at 2.13 GHz. Scripts are generated for the simulator to be able to run in batch mode, allowing the CPU to run with less resources than running the simulator with a graphical user interface (GUI). To be able to benchmark the simulation run-time, Tcl scripts are created with processes which evaluate system time at the beginning and end of the simulation.

**Figure 15: RTL Simulation Test Environment**

Two types of HDL simulation will be run: one run without profiler disabled and one with profiler enabled. The disabled profiler run, allows us to verify functionality and ensure the circuit is operating correctly, but does not allow us see the communication bottleneck between the DUT and the testbench. Since there are  $2^n$  possible vectors to be fed as primary inputs, profiler information is needed to assess the possible speedup that can be attained in simulation acceleration.

## **Simulation Acceleration**

To reduce the number of events occurring in the CPU, the DUT will be transferred to the FPGA hardware, and will connect physically to the workstation via PCIe connector. The PCIe connector will facilitate information serially between the hardware and simulator via a cosimulation interface. With this methodology, there are two portions of the HDL code: synthesizable and non-synthesizable.

| Synthesizable (Implemented on FPGA) | Non-Synthesizable (Remains in HDL |  |

|-------------------------------------|-----------------------------------|--|

|                                     | Simulator)                        |  |

| Ports                               | Delay statements                  |  |

| Signals and variables               | Device initialization             |  |

| Procedures                          | Assign statements                 |  |

| Modules                             | User defined primitives           |  |

| Functions                           | Force and release                 |  |

| Tasks                               | Time constructs                   |  |

Table 2: Synthesizable vs. Non-Synthesizable Logic

The DUT portion of the system (ISCAS S400) is a Verilog gate-level netlist, with a scan flip flop module inserted. Since the DUT is fully synthesizable, it is able to me mapped to FPGA LUTs and implemented onto hardware. The testbench however contains numerous non-synthesizable constructs which aid in the debugging process in addition to the waveform and schematic view. Such tasks include system functions (\$display, \$strobe, \$finish, etc.) which allow output from the design to the simulator console, which can be dumped to a text file for offline debug. Scan chain vectors are fed in through dedicated test pins from external sources, so the test environment must simulate this correctly. The external source in this case will be the HDL simulator, which will serially input the vectors into each scan register in the DUT implemented onto the FPGA board (Figure 16). The resultant vector will feed out back to the testbench which will be outputted onto the console and waveform viewer.

Figure 16: Simulation Acceleration Test Enviornment

Figure 17 below displays the separation between the system components which are non-synthesizable and synthesizable. The emulation compiler, Aldec Hardware Emulation Solutions Design Verification Manager [22], automatically analyzed RTL sources, and distinguishes between code which will remain in the simulator, and code which will be implemented onto HW. The DUT is fully synthesizable and implemented to FPGA LUTs, while the testbench constructs remain in the HDL simulator. For this design, the non-synthesizable constructs include: Clock generation, Reset sequence, Scan Sequence, and Scan Enable Sequence. The sequences are described more in detail in the previous section describing the testbench. The communication between the HDL simulator and DUT are signal-based, meaning a single bit is transferred over a single-ended (SE) IO line available on the FPGA. The design has 7 inputs and 7 outputs, requiring a total of 14 SE IO, but the speed of the simulation is dictated by the transferring of data

on these lines.

Figure 17: Splitting RTL Simulation Environment for Simulation Acceleration

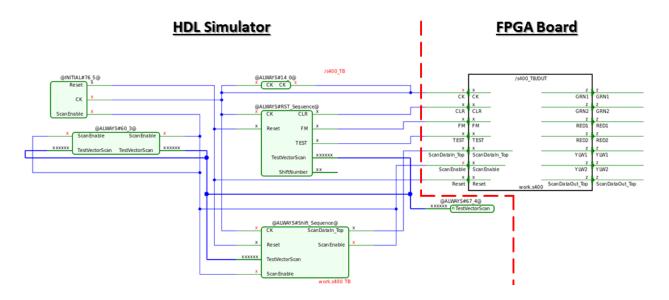

The advantage of using simulation acceleration is that the pre-existing testbench from RTL simulation can be reused. This is beneficial to SoC design teams which are separated into design and verification units, as there requires no modification to port the design to an acceleration system. Since the testbench containing all test sequences are already defined [16], they are ported directly into the emulator for analysis. The complete process for simulation acceleration is shown in Figure 13 below [23]. The design import stage of acceleration allows importing the FPGA design libraries or simulation libraries which were used during RTL simulation. Each file in the library in analyzed by the emulator, and automatically determines the synthesizable and non-synthesizable code. After the code is analyzed, the user selects a top-level instance, and configures the emulation options in the second stage. A user can instrument debug probes, partition design instances in multiple FPGAs, and synthesize the DUT with selected options with FPGA vendor tools. After running a place-and-route process, which physically maps the design to FPGA primitives, scripts are automatically generated which instantiate the communication between the hardware and simulator.

**Figure 18: Emulation Setup Flow**

### **Transaction-Based Emulation**

To utilize transaction-based emulation, there needs to be modification to the done on the hardware and software side. The pre-existing testbench cannot be used, since the interface SCE-MI interface uses transactions for communication, as opposed to signals in simulation acceleration.

### Software Side Modifications

- 1. **SystemC Testbench** The biggest change of the test environment will be converting the testbench sequences to high-level SystemC constructs. Whereas the RTL testbench relied on events such as the rising edge of a clock, the SystemC testbench focus more towards the implementation of the sequence, rather than its trigger events. This will be done through two primary functions: timulus and read. The purpose of the stimulus function is to generate all test sequences defined from the RTL testbench. Using C/C++ constructs they are converted to high-level implementation. The sequences are converted as follows:

- a. Clock Generation The clock sequence no longer needs to be implemented in the testbench since the SCE-MI standard defines clock operations with the uncontrolled clock and controlled clock. Since the clock itself is required for hardware operation, two clock related ports must be defined to operate correctly:

- clock port and clock control. These two ports are directly synthesized onto the FPGA, and have parameters which can be modified for multiple clocks, positive/negative edge triggers, duty cycle, and phase.

- b. Reset Toggle Similar to clock generation, SCE-MI defines the reset sequence of the system with and uncontrolled and controlled reset parameter. The reset signals are defined in the clock control and clock port, which are directly synthesized onto the FPGA. User can modify HDL parameters to define the length of the reset sequence.

- c. Scan Enable Toggle The scan enable toggle sequence is accomplished by generating a 7-bit vector (similar implementation to RTL simulation/acceleration), and setting the scan enable input high. For the TDI value, a value of 0x1 is shifted in after the reset. The data in the scan chain is shifted out, and verified when received by the results function in the testbench. After the reset sequence, all scan registers should have a value 0x0, and by shifting a value of 0x1 into chain, it verifies all registers can change states correctly. The stimulus function outputs are shown in following table:

| Test Sequence      | Stimulus Function                                | Results Function                |

|--------------------|--------------------------------------------------|---------------------------------|

| Clock Generation   | N/A                                              | N/A                             |

|                    | (SCE-MI defines system clocks)                   | (SCE-MI defines system          |

|                    |                                                  | clocks)                         |

| Reset Toggle       | N/A                                              | N/A                             |

|                    | (SCE-MI defines Reset )                          | (SCE-MI defines Reset )         |

|                    | -Scan Enable = 0 →1                              | Read output vector from         |

| Scan Enable Toggle | -Test Mode = $0 \rightarrow 1$                   | message proxy, and display to   |

|                    | -Primary IO = X                                  | output string construct. Verify |

|                    | -Send testbit '1'                                | bit vector is of value '1'.     |

|                    | -Scan Enable= 1 →0                               |                                 |

|                    | -Scan Enable = 0 →1                              | Read output vector from         |

|                    | -Test Mode = $0 \rightarrow 1$                   | message proxy, and display to   |

| Scan Sequence      | -Primary IO = X                                  | output string construct         |

|                    | -input all bit of first test vector              |                                 |

|                    | serially to TDI pin with FOR loop                |                                 |

|                    | -Scan Enable = 1 →0                              |                                 |

|                    | -Increment test vector                           |                                 |

|                    | -Loop last 3 steps for all 2 <sup>n</sup> vector |                                 |

**Table 3: Test Sequences**

d. *Scan Sequence* – After the scan enable sequence, the shift register has been verified to switch reach the 0 state (reset sequence) and 1 state (scan enable sequence). For this SystemC testbench, there is a 7-bit message which will be sent to the hardware side. One of the inputs is a dedicated scan in port, which a

21-bit test vector will be serially shifted in. In Figure 19 on the left below, shows the shift and write sequence controlled by a FOR loop construct. The data is first shifted into hardware, and written to the message port. In the next section, a FSM is added to decrease the number of write tasks to the hardware. After the FOR loop has finished for all 21 bits, the data is checked if all 2<sup>21</sup> combinations have been exercised, and if not, the testbench deasserts the scan enable, and increments the test vector (shown in Figure 19 on the right).

```

for (int i = 0; i < 21; i++)

{

// Shift-in test vector & write message

inportMessage[2] = TestVector[i];

xtor.TrInPort->write(inportMessage);

}

else

{

//De-assert Scan Enable & write message

inportMessage[1] = 0;

xtor.TrInPort->write(inportMessage);

TestVector = TestVector + 1;

inportMessage[1] = 1;

xtor.TrInPort->write(inportMessage);

```

Figure 19: Testbench Scan Sequence

2. SCE-MI Software Infrastructure Implementation —The software implementation of the SCE-MI infrastructure includes the message ports, service handlers, error detection, and other SCE-MI functionality. The Aldec HES-DVM emulator contains all necessary C/C++ files for implementing the SCE-MI software infrastructure [22]. The main focus of the end user (verification team/design team), is to create the high-level testbench and the transactor with hardware implementation. For this portion, the software SCE-MI implementation has been tested and verified to operate correctly.

### Hardware Side Modifications

### 1. Transactor development

a. *Transactor core* – The transactor core receives the transactions from the software side (inMessage) and sends them to the DUT as signals. For this implementation,

the SystemC testbench controls the shift sequence with a FOR loop, so data from the transactor core is passed connected directly to the DUT. This is sometimes referred to as a 'dummy' transactor (shown in Figure 20), since there is no manipulation of data in the transactor core. In the next section, I will describe a FSM implementation in HW, which will decrease communication for bit shifts into the DUT.

```

elsif(rising edge(Uclock)) then

if (dataReady = '1') then

out xtor to DUT GND Reg

<= inMsgVect(7);

out_xtor_to_DUT_VDD_Reg

<= inMsgVect(6);

<= inMsgVect(5);

out xtor to DUT FM Reg

out xtor to DUT TEST Reg

<= inMsgVect(4);

out xtor to DUT CLR Reg

<= inMsgVect(3);

out_xtor_to_DUT_ScanDataIn_Top_Reg <= inMsgVect(2);</pre>

<= inMsgVect(1);

out xtor to DUT ScanEnable Reg

out xtor to DUT ScanTestMode Reg

<= inMsgVect(0);

end if;

end if;

```

Figure 20: Transactor Pass Through Assignments

b. SCE-MI Message Ports – The message port consists of an inPort and outPort. The outPort sends data from the transactor to the software side, and the inPort receives data from the software side to the transactor core. The message ports utilize a dual ready handshake protocol with three primary I/O's: ReceiveReady, TransmitReady, and message as shown in Figure 21 below.

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity SceMiMessageInPort is

generic( PortWidth: natural; PortDepth: natural := 64 );

port(

ReceiveReady: in std_logic; TransmitReady: out std_logic;

Message: out std_logic_vector( PortWidth-1 downto 0 ) );

end;

```

Figure 21: SCE-MI Message In-Port

When both the ReceiveReady and TransmitReady are asserted high, the message is sent to the destination across the channel. This occurs on the active edge of the Uclock, which allows the ports to be written and read to while DUT is still in operation. On the software side, when a message port is instantiated (whether it be in or out) in the testbench, a first-in first-out memory is created where instructions are stored prior to entering and leaving the proxy. The instruction from the testbench is sent to the FIFO, where the proxy will wait for the ReceiveReady on the hardware side. The proxy will assert a TransmitReady (for an inPort) or ReceiveReady (for an outPort) when the FIFO contains data, and flush the data out, when ready on the hardware side. Figure 22 below is the C++ implementation of the SCE-MI InPort developed by Aldec which is used in the SystemC TB.

```

//Read input FIFO.

inData = InPort.read();

//Create data structure for port.

for(unsigned int wrd = 0; wrd < IN_PORT_SIZE/32; wrd++)

{

scemi_msg.Set(wrd, (SceMiU32) inData.range( (32*(wrd+1))-1, 32*wrd).to_uint)}

// Wait for data port to be ready

InPortReady.wait();

PRINT_DEBUG << "Scemi Port: " << name() << " sends data: " << inData.to_string(s)

//Send data.

InPortProxy -> Send(scemi_msg);

```

Figure 22: SCE-MI Message In-Port Software Implementation

- c. SCE-MI Clock Port The SCE-MI clock port provides the DUT with a controlled reset and clock. Through a set of parameters such as clock duty, clock ratio, phase, and reset cycles, the user can customize how timing and reset is handled in the circuit. For circuits with multiple clock frequencies, multiple clock ports have to be instantiated with parameters customized for each clock frequency. Since the system used in this thesis contains only a single global clock, one clock port and clock control is needed. If no parameters for the clocking are set, SCE-MI automatically generates a 1/1 ratio clock, a single clock with the highest frequency in the system. Most of the time, SCE-MI will grab this clock from oscillators available on the emulation board. Each EDA vendor provides the input clock for SCE-MI based on tests and delay analysis on a specific FPGA board. The end-user need not focus on the clock implementation in the HW, but only create the necessary clock port, which will call the correct frequency built on the emulation API.

- d. SCE-MI Clock Control The SCE-MI clock control macro is a macro which aligns clock edges from the uncontrolled clock and controlled clock. This clock control enables freezing the DUT controlled clock, while still operating the

transactor to receive incoming data from the software side. The main advantage of this control module, which will be used in the modified core implementation, is the ability to perform operations on data while the DUT is still 'frozen'. ReadyForCclock is a signal in the control module that allows the DUT clock to advance. If data received from the software of the DUT needs to be analyzed, ReadyForCclock can be set low, which allows operation on the data from the DUT or software side to occur without the DUT clock running.

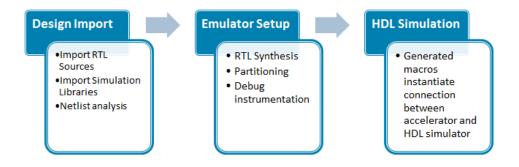

To implement the transaction-based approach, there needs to be multiple changes in the hardware and software environment. This can be difficult, if verification teams are not accustomed to emulation environment. Standards such as SCE-MI continue to evolve, as verification teams adopt the standard to speed up verification for multimillion gate SoC. With all the changes to the test environment, the block level of the system is shown in Figure 23 below. Two proxies will be instantiated on the software side, which will be to pass transactions to and from the HW. A C++ function called 'Stimulus', will generate all the necessary signals, and generate the test vector which will be serially shifted into the inPort on the hardware side. The serial shifting is occurring in the software and is sent bit by bit to the inPort. This method will show that even though the transactor core and testbench is not optimized, it still incurs a speedup due to the high-level testbench and hardware implementation. The inPort will pass through a dummy transactor on the active edge of Uclock (which pauses the Cclock operating the DUT), and be sent directly to the IO of the DUT. The transactor will then activate Cclock, allowing the DUT data to propagate to the output signals. The output data is passed to the outPort, where it is serialized into a single bit vector, and sent to a Read function which analyzed the data and displays on the user console. The data can be stored in an output text file for later future analysis.

Figure 23: SCE-MI Pass Through Test Environment

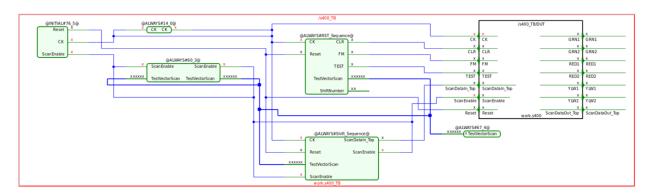

## **Modified Transaction-Based Emulation**

For the next implementation, we will modify the previous approach by adding data manipulation inside the transactor core. Previously a 21-bit vector was generated in the software and serially shifted via a FOR loop to the dummy transactor core, which passed it directly to the DUT. For the modified implementation, the test vector will be generated in the software, but the entire vector will be within the message sent to the transactor core. This cuts out the serial processing of each bit to the inPort, and the number of writes/reads between the HW/SW interfaces. The message vector and signals will pass through the transactor core, which contains a FSM (Figure 24 below) that will serially shift data in to the DUT.

Figure 24: SCE-MI FSM Test Environment

The FSM machine (Figure 25), which is regulated by Uclock, will contain multiple state for all inPort/outPort calls, vector reads, and shifting. As the FSM cycles through all the states, the scan control signals also regulate the flow of data to the scan chain, as opposed to being in the testbench in the previous implementation. The inPort/outPort calls regulate the dual ready handshake protocol, which asserts appropriate signals before and after the shift sequence. After the shift sequence has finished, the output port transmits data, while new data is called to the inPort simultaneously. After new data is received the shift sequence begins again. The FSM must be reset appropriately, so all signals are initialized. The Ureset initializes all signals prior to the data exchange sequence between the hardware and software. This ensures that the FSM does not begin in an unknown state.

```

FSM:process (Ureset, Uclock)

begin

if(Ureset = '1') then

<= '0';

out xtor to DUT FM Reg

out_xtor_to_DUT_TEST_Reg

out_xtor_to_DUT_CLR_Reg

<= '0';

<= '0';

out xtor to DUT ScanDataIn Top Reg <= '0';

out_xtor_to_DUT_ScanEnable_Reg <= '0';

elsif(rising_edge(Uclock)) then

if (CS = InPortCall) then

CS <= VectorReceived;

OutportReady2Send <= '0';

InportReady2Receive <= '1';</pre>

elsif (CS = VectorReceived) then

<= Shift0:

InportReady2Receive

<= '0';

OutportReady2Send

<= '1';

out xtor to DUT FM Reg

<= inMsgVect(23);

out_xtor_to_DUT_FM_Reg

out_xtor_to_DUT_TEST_Reg

out_xtor_to_DUT_CLR_Reg

<= inMsgVect(22);

<= inMsgVect(21);

out xtor to DUT ScanEnable Reg

<= '1';

elsif (CS = Shift0) then

CS <= Shift1:

out xtor to DUT ScanDataIn Top Reg <= inMsgVect(0);

elsif (CS = Shift1) then

CS <= Shift2;

out xtor to DUT ScanDataIn Top Reg <= inMsgVect(1);

```

**Figure 25: Transactor FSM Transitions**

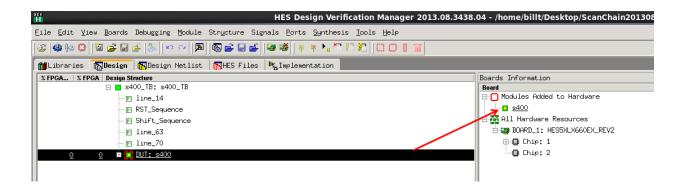

## FPGA-based Emulator [22]

The FPGA-based prototype solution which will be used for this thesis is the Aldec HES5XLX660EX (Figure 26 below), which utilizes two Xilinx XC5VLX330T FPGAs for a total capacity of 5 million ASIC gates. Users are able to connect the HES5 board to a host workstation via PCI Express x8 lane communication. A dedicated FPGA provides host interface logic when connecting the Aldec HES-DVM emulator with the FPGA prototyping board. On the board are two SO-DIMM sockets, which users can utilize up to 2GB of DDR2 memory for memory expansion. Also available are external clock inputs, on-board oscillators, and PLL circuitry for users to implement different clocking schemes in their SoC designs. Users can utilize daughterboard SAMTEC connectors, each with 124 LVDS to connect external targets to the FPGA prototyping board. Since the DUT is fairly small, no partitioning will be needed which enables faster speed. If partitioning was required (large number of IO or large design capacity), the HES-5 provides 428 SE/ 219 LVDS IO for inter-FPGA communication. The data would need

some serial/de-serialization methodology which would enable multiple signals to be processes over a single IO or LVDS pair.

Figure 26: Aldec HES-5 Prototyping Board

# **Results & Analysis**

## **RTL Simulation Results**