UNLV Theses, Dissertations, Professional Papers, and Capstones

8-1-2012

# CPU Scheduling for Power/Energy Management on Heterogeneous Multicore Processors

Rajesh Patel *University of Nevada, Las Vegas*, patel2@unlv.nevada.edu

Follow this and additional works at: https://digitalscholarship.unlv.edu/thesesdissertations

Part of the Computer and Systems Architecture Commons, and the Computer Sciences

Commons

#### **Repository Citation**

Patel, Rajesh, "CPU Scheduling for Power/Energy Management on Heterogeneous Multicore Processors" (2012). UNLV Theses, Dissertations, Professional Papers, and Capstones. 1691.

https://digitalscholarship.unlv.edu/thesesdissertations/1691

This Dissertation is brought to you for free and open access by Digital Scholarship@UNLV. It has been accepted for inclusion in UNLV Theses, Dissertations, Professional Papers, and Capstones by an authorized administrator of Digital Scholarship@UNLV. For more information, please contact digitalscholarship@unlv.edu.

# CPU SCHEDULING FOR POWER/ENERGY MANAGEMENT ON HETEROGENEOUS MULTICORE PROCESSORS

By

#### Rajesh Patel

Bachelor of Science in Biological Sciences University of Southern California 1991

Bachelor of Science in Nuclear Medicine University of Nevada, Las Vegas 1999

Master of Science in Computer Science University of Nevada, Las Vegas 2005

A dissertation submitted in partial fulfillment of the requirements for the

Doctor of Philosophy in Computer Science

School of Computer Science Howard R. Hughes College of Engineering The Graduate College

University of Nevada, Las Vegas August 2012

Copyright by Rajesh Patel, 2012 All Rights Reserved

#### THE GRADUATE COLLEGE

We recommend the dissertation prepared under our supervision by

Rajesh Patel

entitled

CPU Scheduling for Power/Energy Management on Heterogeneous Multicore Processors

be accepted in partial fulfillment of the requirements for the degree of

# **Doctor of Philosophy in Computer Science**

School of Computer Science

Ajoy K. Datta, Committee Chair

Lawrence Larmore Committee Member

Yoohwan Kim, Committee Member

Venkatesan Muthukumar, Committee Member

Wolfgang Bein, Graduate College Representative

Tom Piechota, Ph.D., Interim Vice President for Research & Dean of the Graduate College

August 2012

#### ABSTRACT

#### CPU Scheduling for Power/Energy Management on Heterogeneous Multicore Processors

by

#### Rajesh Patel

Dr. Ajoy K. Datta, Examination Committee Chair School of Computer Science University of Nevada, Las Vegas

Power and energy have become increasingly important concerns in the design and implementation of today's multicore/manycore chips. Many methods have been proposed to reduce a microprocessor's power usage and associated heat dissipation, including scaling a core's operating frequency. However, these techniques do not consider the dynamic performance characteristics of an executing process at runtime, the execution characteristics of the entire task to which this process belongs, the process's priority, the process's cache miss/cache reference ratio, the number of context switches and CPU migrations generated by the process, nor the system load. Also, many of the techniques that employ dynamic frequency scaling can lower a core's frequency during the execution of a non-CPU intensive task, thus lowering performance. In addition, many of these methods require specialized hardware and have not been tested upon real hardware that is widely available, including the recent AMD or Intel multicore chips.

One problem dealing with power/energy management for heterogeneous multicore processors is: Given a set of processes, each having identical default priorities, in a given task to be executed by a heterogeneous multicore/manycore processor system, schedule each process in this task to execute upon the CPU(s) in this system such that the global power budget is minimized, yet the performance gain of all processes is maximized, and the performance loss of all processes is minimized. Doing so, in a scenario where each process has a different (not necessarily unique) static or dynamic (but not necessarily the default) priority, without adversely affecting process completion order, as dictated by process priority is

yet another problem. Finally, utilizing the cache miss/cache reference ratio and the number of context switches and CPU migrations as scheduling criteria are two other problems. This dissertation will elaborate upon these four problems, and will describe our four approaches to solving these problems.

#### ACKNOWLEDGMENTS

I would like to offer a special thanks to my dissertation advisor, Dr. Ajoy K. Datta, for chairing my committee and advising me throughout my dissertation work. His patience, support, enthusiasm, and most importantly, his confidence in my abilities, have helped me greatly throughout my graduate study. I am also very grateful to Dr. Wolfgang Bein, Dr. Lawrence Larmore, Dr. Yoohwan Kim, and Dr. Venkatesan Muthukumar for their participation in my committee.

This dissertation is dedicated to my parents and family. Their support, love, and faith in my abilities were very important for completing this dissertation research.

# TABLE OF CONTENTS

| ABSTRACT                                                                                                                               | iii                     |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| ACKNOWLEDGEMENTS                                                                                                                       | v                       |

| LIST OF TABLES                                                                                                                         | viii                    |

| LIST OF FIGURES                                                                                                                        | X                       |

| CHAPTER 1 INTRODUCTION                                                                                                                 | 1<br>3<br>4             |

| CHAPTER 2 MULTICORE PROCESSORS  Overview  Development  Overview of Architecture  Homogeneous versus Heterogeneous Multicore Processors | 6<br>6<br>7<br>10<br>11 |

| CHAPTER 3 MULTICORE PROCESSOR IMPLEMENTATION CHALLENGES Cache Coherence Power and Temperature Management Multicore Performance         | 13<br>13<br>14<br>16    |

| CHAPTER 4 POWER/ENERGY CPU SCHEDULING PROBLEM FOR HETEROGENEOUS MULTICORE PROCESSOR SYSTEMS  Motivation                                | 18<br>18<br>20<br>23    |

| CHAPTER 5 ALGORITHM 1: Algorithm CPU Scheduler                                                                                         | 25<br>25<br>27<br>31    |

| CHAPTER 6 ALGORITHM 2: Algorithm Priority CPU Scheduler                                                                                | 33<br>33<br>35<br>40    |

| CHAPTER 7 ALGORITHM 3: Algorithm Cache Miss Priority CPU Scheduler                                                                     | 42                      |

| Description of Algorithm Cache Miss Priority CPU Scheduler Algorithm 3 Cache Miss Feedback-driven Priority-based CPU Scheduling Algorithm (Cache Miss Priority CPU Scheduler) | 42<br>44<br>49 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CHAPTER 8 ALGORITHM 4: Algorithm Context Switch Priority CPU Scheduler                                                                                                        | 51             |

| Variables and Constants Used in Algorithm Context Switch Priority CPU  Scheduler                                                                                              | 51             |

| Description of Algorithm Context Switch Priority CPU Scheduler Algorithm 4 Context Switch Feedback-driven Priority-based CPU Scheduling Al-                                   | 53             |

| gorithm (Context Switch Priority CPU Scheduler)                                                                                                                               | 59             |

| CHAPTER 9 EVALUATION AND RESULTS                                                                                                                                              | 61             |

| Methodology                                                                                                                                                                   | 61             |

| Discussion of Results                                                                                                                                                         | 63             |

| Evaluation of Algorithm $CPU$ $Scheduler$                                                                                                                                     | 64             |

| Evaluation of Algorithm Priority CPU Scheduler                                                                                                                                | 72             |

| Evaluation of Algorithm Cache Miss Priority CPU Scheduler                                                                                                                     | 94             |

| Evaluation of Algorithm Context Switch Priority CPU Scheduler                                                                                                                 | 105            |

| CHAPTER 10 CONCLUSION AND FUTURE RESEARCH                                                                                                                                     | 115            |

| BIBLIOGRAPHY                                                                                                                                                                  | 118            |

| $VIT\Lambda$                                                                                                                                                                  | 191            |

# LIST OF TABLES

| Table 1  | Benchmarks and Tasks Evaluated                                          | 64 |

|----------|-------------------------------------------------------------------------|----|

| Table 2  | Performance of Benchmarks Evaluated for Algorithm 1                     | 65 |

| Table 3  | Performance, Performance per Watt, and Execution Time · Watt            |    |

|          | for Tasks 1, 2, 3, and 4                                                | 67 |

| Table 4  | Total Power Savings, Percent Power Savings, and Percent                 |    |

|          | Improvement of Performance, Performance per Watt, and                   |    |

|          | Execution Time · Watt for Tasks 1, 2, 3, and 4                          | 69 |

| Table 5  | Completion Order of Benchmarks Evaluated (static priorities             |    |

|          | noncpuintensive benchmarks higher priority)                             | 74 |

| Table 6  | Completion Order of Benchmarks Evaluated (static priorities             |    |

|          | noncpuintensive benchmarks lower priority)                              | 74 |

| Table 7  | Completion Order of Benchmarks Evaluated (dynamic priorities)           | 74 |

| Table 8  | Completion Order of Benchmarks Evaluated for Task 4                     | 75 |

| Table 9  | Performance of Benchmarks Evaluated (static priorities                  |    |

|          | noncpuintensive benchmarks higher priority) for Algorithm 2             | 78 |

| Table 10 | Performance of Benchmarks Evaluated (static priorities                  |    |

|          | noncpuintensive benchmarks lower priority) for Algorithm 2              | 78 |

| Table 11 | Performance of Benchmarks Evaluated (dynamic priorities) for            |    |

|          | Algorithm 2                                                             | 78 |

| Table 12 | Performance, Performance per Watt, and Execution Time $\cdot$ Watt      |    |

|          | for Tasks 1, 2, 3, and 4 (static priorities noncpuintensive             |    |

|          | benchmarks higher priority)                                             | 84 |

| Table 13 | Performance, Performance per Watt, and Execution Time $\cdot$ Watt      |    |

|          | for Tasks 1, 2, 3, and 4 (static priorities noncpuintensive             |    |

|          | benchmarks lower priority)                                              | 84 |

| Table 14 | Performance, Performance per Watt, and Execution Time $\cdot$ Watt      |    |

|          | for Tasks 1, 2, 3, and 4 (dynamic priorities)                           | 84 |

| Table 15 | Total Power Savings, Percent Power Savings, and                         |    |

|          | Percent Improvement of Performance, Performance per Watt, and           |    |

|          | Execution Time $\cdot$ Watt for Tasks 1, 2, 3, and 4 (static priorities |    |

|          | noncpuintensive benchmarks higher priority)                             | 89 |

| Table 16 | Total Power Savings, Percent Power Savings, and Percent                 |    |

|          | Improvement of Performance, Performance per Watt, and                   |    |

|          | Execution Time · Watt for Tasks 1, 2, 3, and 4 (static priorities       |    |

|          | noncpuintensive benchmarks lower priority)                              | 89 |

| Table 17 | Total Power Savings, Percent Power Savings, and Percent                 |    |

|          | Improvement of Performance, Performance per Watt, and                   |    |

|          | Execution Time Watt for Tasks 1, 2, and 3 (dynamic priorities)          | 89 |

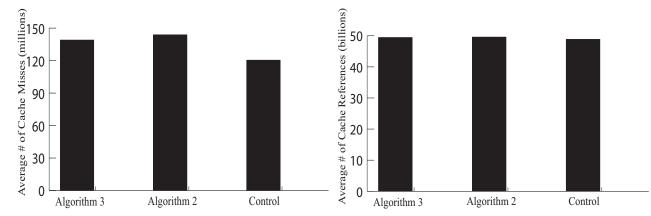

| Table 18 | Average Number of Cache Misses, Cache References, and Average           |    |

|          | Cache Miss/Reference Ratio for Algorithms 3, 2, and Control             | 97 |

| Table 19 | Performance, Performance per Watt, and Execution Time Watt                 |     |

|----------|----------------------------------------------------------------------------|-----|

|          | for Task 4 (dynamic priorities)                                            | 100 |

| Table 20 | Total Power Savings, Percent Power Savings, and Percent                    |     |

|          | Improvement of Performance, Performance per Watt, and                      |     |

|          | Execution Time $\cdot$ Watt by Algorithm 3 for Task 4 (dynamic priorities) | 100 |

| Table 21 | Percent Reduction of Average Number of Cache Misses, Cache                 |     |

|          | References, and Average Cache Miss/Reference Ratio over Control            |     |

|          | by Algorithms 3 and 2 and over Algorithm 2 by Algorithm 3 $\dots$          | 103 |

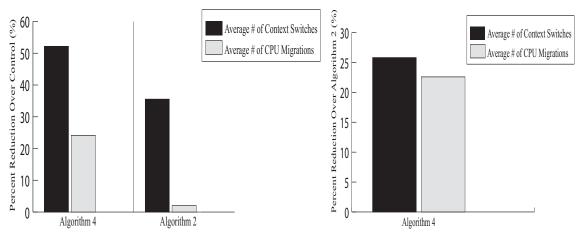

| Table 22 | Average Number of Context Switches and CPU Migrations for                  |     |

|          | Algorithms 4, 2, and Control                                               | 108 |

| Table 23 | Performance, Performance per Watt, and Execution Time $\cdot$ Watt         |     |

|          | for Task 4 (dynamic priorities)                                            | 110 |

| Table 24 | Total Power Savings, Percent Power Savings, and Percent                    |     |

|          | Improvement of Performance, Performance per Watt, and                      |     |

|          | Execution Time $\cdot$ Watt by Algorithm 4 for Task 4 (dynamic priorities) | 110 |

| Table 25 | Percent Reduction of Average Number of Context Switches and                |     |

|          | CPU Migrations over Control by Algorithms 4 and 2 and over                 |     |

|          | Algorithm 2 by Algorithm 4                                                 | 113 |

# LIST OF FIGURES

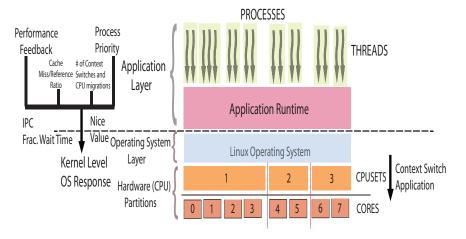

| Figure 1   | General Overview of Algorithms 1 - 4                                                                                     | 4   |

|------------|--------------------------------------------------------------------------------------------------------------------------|-----|

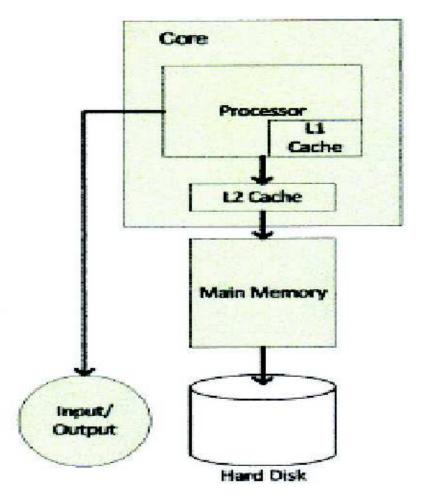

| Figure 2   | Basic Microprocessor Design                                                                                              | 8   |

| Figure 3   | Shared Memory Model (left) and Distributed Memory Model                                                                  |     |

|            | (right)                                                                                                                  | 9   |

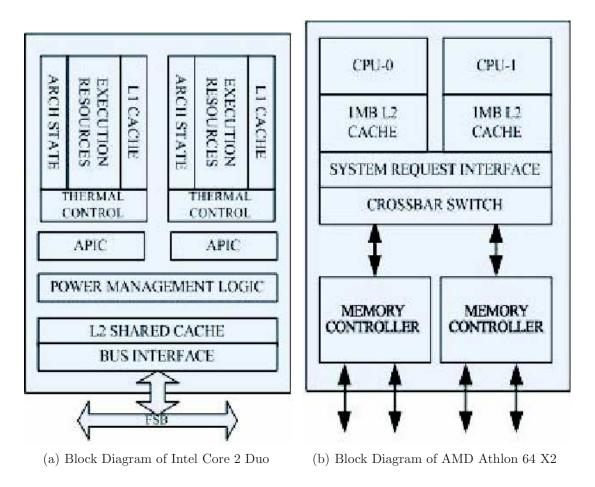

| Figure 4   | Block Diagrams of the Core 2 Duo and Athlon 64 X2 multicore                                                              |     |

|            | processors                                                                                                               | 10  |

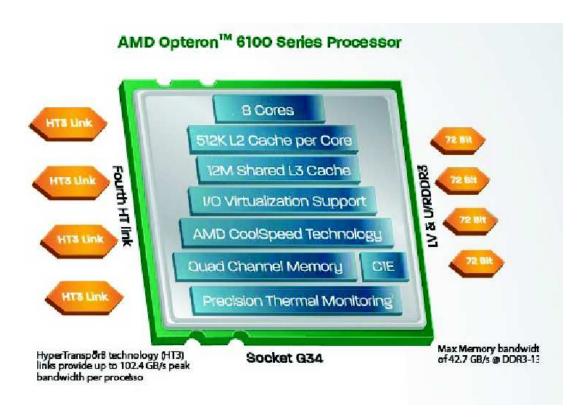

| Figure 5   | Block Diagram of AMD Opteron 6100 processor                                                                              | 11  |

| Figure 6   | Relationship Between Core Operating Frequency and Power                                                                  |     |

|            | Consumption                                                                                                              | 14  |

| Figure 7   | Hardware Partitioning                                                                                                    | 62  |

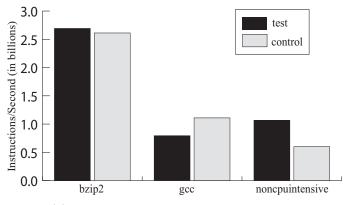

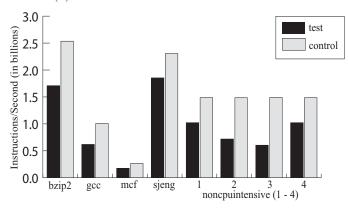

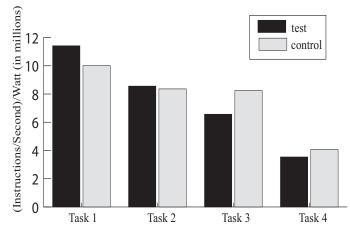

| Figure 8   | Performance of Benchmarks Evaluated for Algorithm 1                                                                      | 66  |

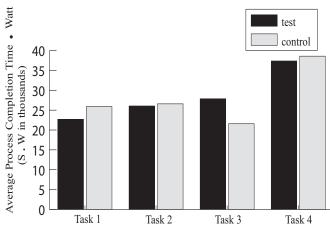

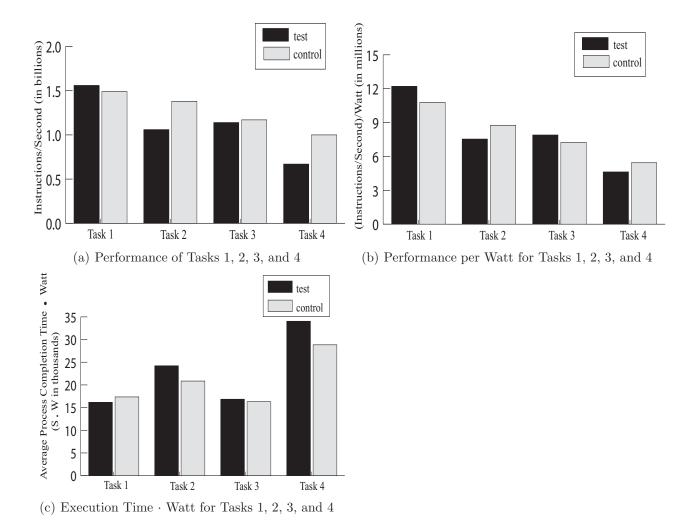

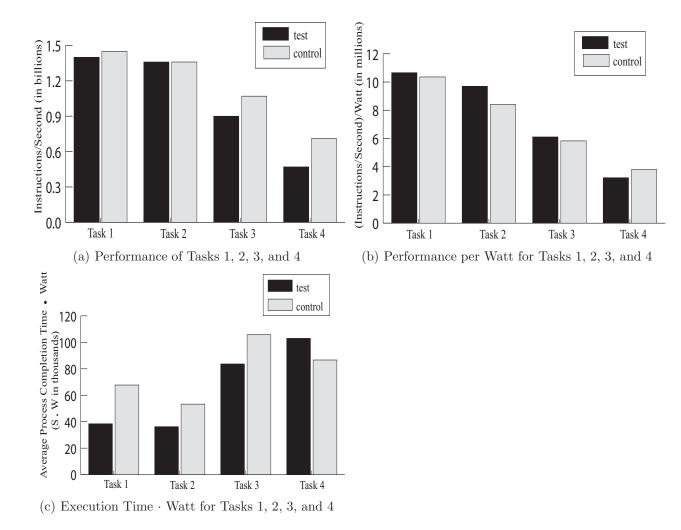

| Figure 9   | Performance, Performance per Watt, and Execution Time · Watt                                                             |     |

| Figure 10  | for Tasks 1, 2, 3, and 4                                                                                                 | 68  |

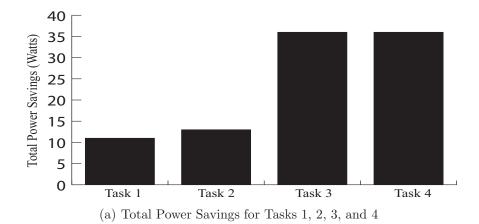

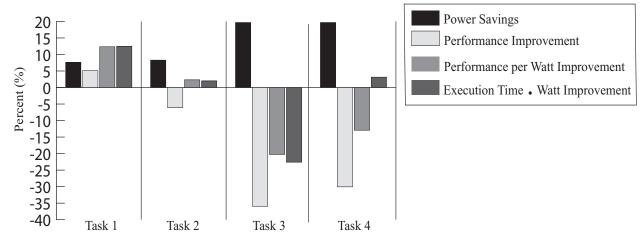

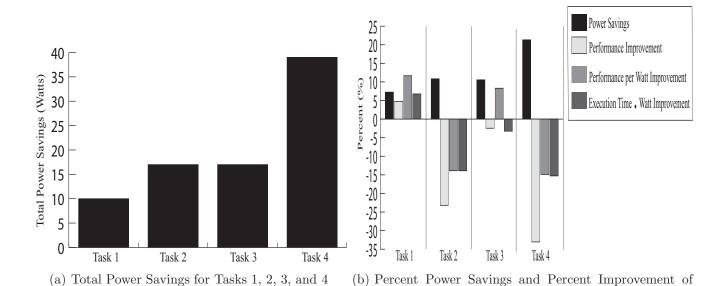

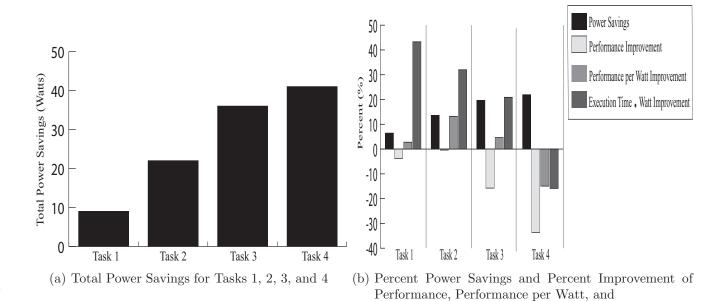

|            | Total Power Savings, Percent Power Savings, and Percent                                                                  |     |

|            | Improvement of Performance, Performance per Watt, and                                                                    |     |

| T. 44      | Execution Time · Watt for Tasks 1, 2, 3, and 4                                                                           | 70  |

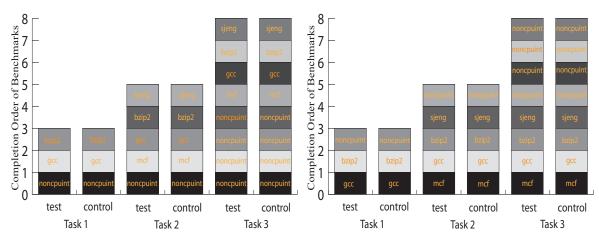

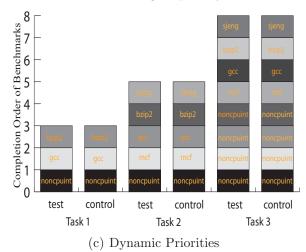

| Figure 11  | Completion Order of Benchmarks Evaluated                                                                                 | 75  |

| Figure 12  | Performance of Benchmarks Evaluated (static priorities                                                                   | =0  |

| T: 10      | noncpuintensive benchmarks higher priority) for Algorithm 2                                                              | 79  |

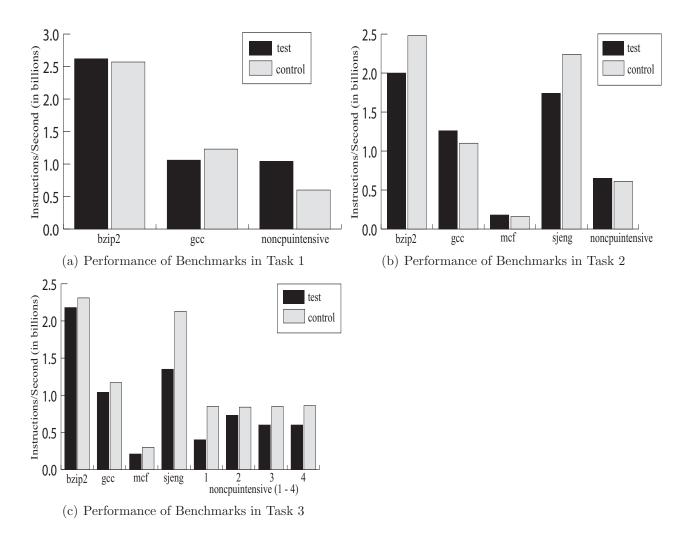

| Figure 13  | Performance of Benchmarks Evaluated (static priorities                                                                   | 0.0 |

| D: 14      | noncpuintensive benchmarks lower priority) for Algorithm 2                                                               | 80  |

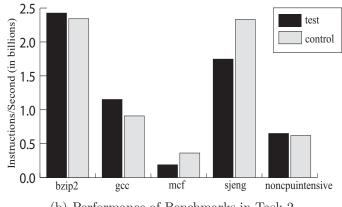

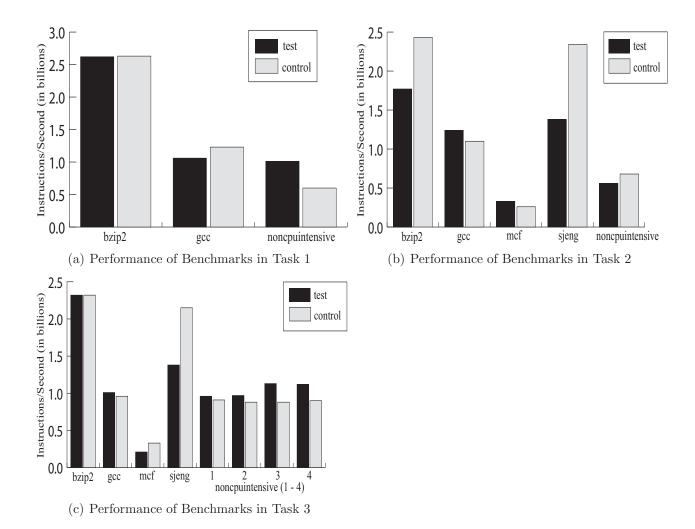

| Figure 14  | Performance of Benchmarks Evaluated (dynamic priorities) for                                                             | 01  |

| D: 15      | Algorithm 2                                                                                                              | 81  |

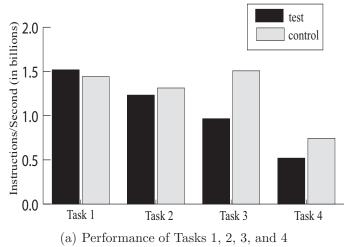

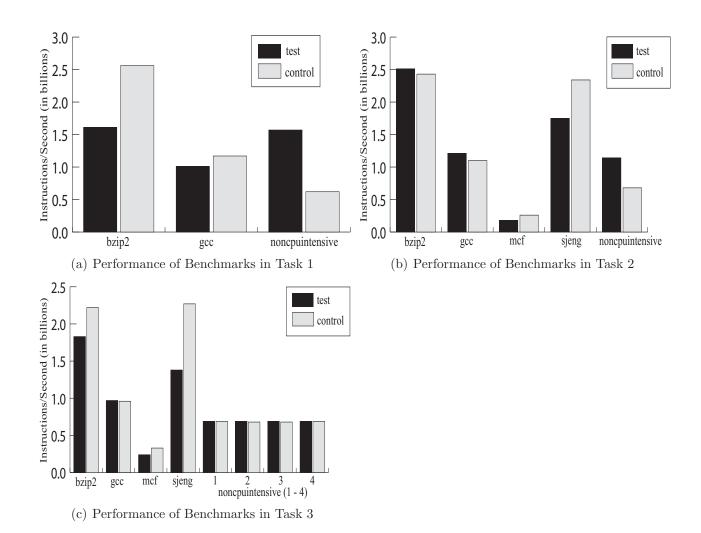

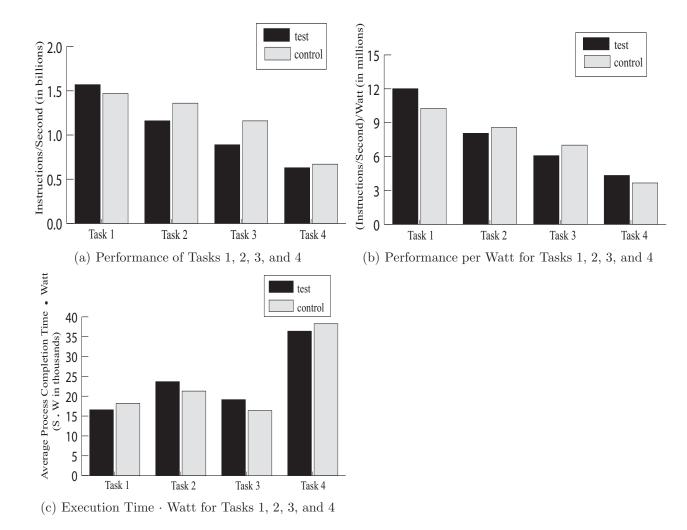

| Figure 15  | Performance, Performance per Watt, and Execution Time · Watt                                                             |     |

|            | for Tasks 1, 2, 3, and 4 (static priorities noncpuintensive                                                              | 85  |

| Figure 16  | benchmarks higher priority)                                                                                              | 00  |

| Figure 16  | Performance, Performance per Watt, and Execution Time · Watt for Tasks 1, 2, 3, and 4 (static priorities noncpuintensive |     |

|            | benchmarks lower priority)                                                                                               | 86  |

| Figure 17  | Performance, Performance per Watt, and Execution Time · Watt                                                             | 00  |

| riguic ii  | for Tasks 1, 2, and 3 (dynamic priorities)                                                                               | 87  |

| Figure 18  | Total Power Savings, Percent Power Savings, and Percent                                                                  | 01  |

| 1 18410 10 | Improvement of Performance, Performance per Watt, and                                                                    |     |

|            | Execution Time · Watt for Tasks 1, 2, 3, and 4 (static priorities                                                        |     |

|            | - noncpuintensive benchmarks higher priority)                                                                            | 90  |

| Figure 19  | Total Power Savings, Percent Power Savings, and Percent                                                                  | 00  |

| riguic 13  | Improvement of Performance, Performance per Watt, and                                                                    |     |

|            | Execution Time · Watt for Tasks 1, 2, 3, and 4 (static priorities                                                        |     |

|            | - noncpuintensive benchmarks lower priority)                                                                             | 91  |

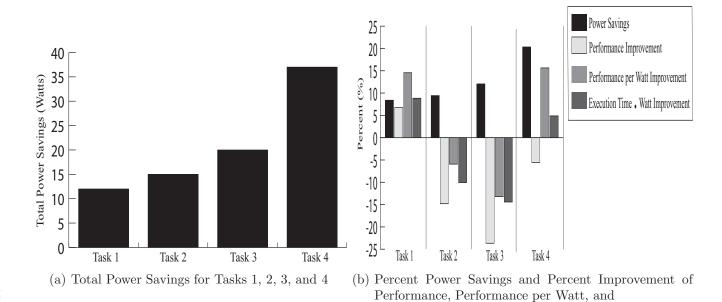

| Total Power Savings, Percent Power Savings, and Percent        |                                                                                                                        |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Improvement of Performance, Performance per Watt, and          |                                                                                                                        |

| Execution Time · Watt for Tasks 1, 2, and 3 (dynamic           |                                                                                                                        |

| ·                                                              | 92                                                                                                                     |

| Average Number of Cache Misses, Cache References, and Cache    |                                                                                                                        |

| Miss/Reference Ratio for Algorithms 3, 2, and Control for Task |                                                                                                                        |

| 4 (dynamic priorities)                                         | 98                                                                                                                     |

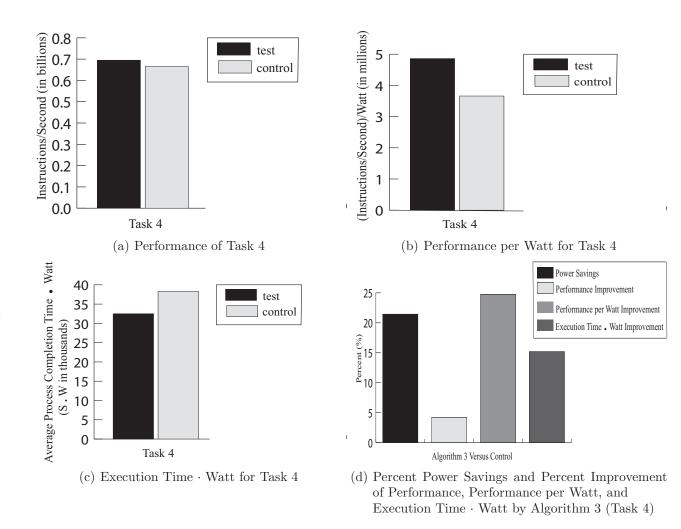

| · · · · · · · · · · · · · · · · · · ·                          |                                                                                                                        |

|                                                                |                                                                                                                        |

| Performance per Watt, and Execution Time · Watt by Algorithm   |                                                                                                                        |

| 3 for Task 4 (dynamic priorities)                              | 101                                                                                                                    |

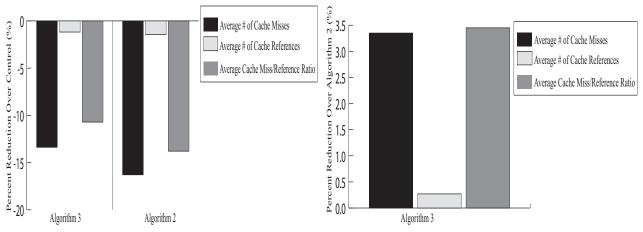

| Percent Reduction of Average Number of Cache Misses, Cache     |                                                                                                                        |

| References, and Average Cache Miss/Reference Ratio over        |                                                                                                                        |

| Control by Algorithms 3 and 2 and over Algorithm 2 by          |                                                                                                                        |

| Algorithm 3                                                    | 104                                                                                                                    |

| Average Number of Context Switches and CPU Migrations for      |                                                                                                                        |

| Algorithms 4, 2, and Control for Task 4 (dynamic priorities)   | 108                                                                                                                    |

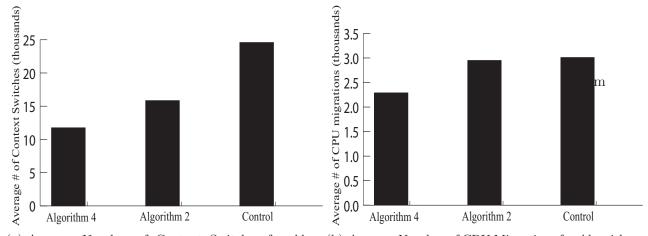

| Performance, Performance per Watt, Execution Time · Watt,      |                                                                                                                        |

| Percent Power Savings, and Percent Improvement of Performance, |                                                                                                                        |

| Performance per Watt, and Execution Time · Watt by Algorithm   |                                                                                                                        |

| 4 for Task 4 (dynamic priorities)                              | 111                                                                                                                    |

| ,                                                              |                                                                                                                        |

| CPU Migrations over Control by Algorithms 4 and 2 and over     |                                                                                                                        |

| Algorithm 2 by Algorithm 4                                     | 113                                                                                                                    |

|                                                                | Improvement of Performance, Performance per Watt, and Execution Time · Watt for Tasks 1, 2, and 3 (dynamic priorities) |

#### CHAPTER 1

#### INTRODUCTION

Recent advances in processor production have led to not only an increase in the number of cores on a single chip, but also a concomitant increase in power consumption and heat dissipation associated with these high performance systems. For example, a 2.8 GHz Intel "Northwood" Pentium 4 chip consumes around 80 W, while a "Prescott" Pentium 4 chip of the same speed consumes around 100 W [24]. This increased power consumption creates an associated increase in heat dissipation, which leads to higher costs for air conditioning, thermal packaging, fans, and electricity. Increased heat and temperature of hardware, such as the CPU, can also lead to decreased longevity and greater incidence of failure of these components. Also, the integration and design of a multicore chip is more difficult to manage, than a lower-density, single-chip design due to thermal constraints [23]. Finally, power savings and decreased heat production can be crucial in notebook computers, where battery life is a constraint and cooling of hardware components is difficult, and in server farms, where even a slight decrease in the power consumption of each server can cause a significant savings for the entire system.

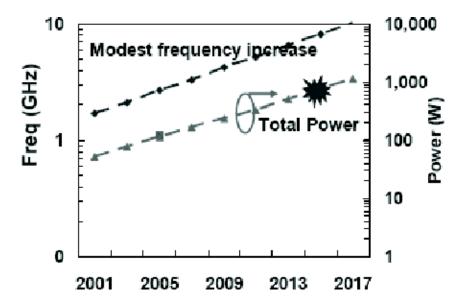

Scaling a CPU's frequency can dramatically affect its power consumption. In fact, the power dissipation at the output pins of a core is directly proportional to its frequency and is governed by the equation

$$P = \frac{1}{2}CV^2 f$$

where f is the effective bus frequency.

CPU frequency scaling may be used to produce an architecture composed of a heterogeneous processor, those with cores operating at different frequencies. Heterogeneous

architectures may achieve a higher performance per watt than comparable homogeneous systems [30, 21] due to the ability of each application to run on a core that best suits its architectural properties. An architecture composed of a heterogeneous processor may contain cores specialized for certain tasks. For example, threads conducting CPU intensive work may execute upon high frequency cores, while threads conducting memory intensive work may execute upon low frequency cores, which consume significantly less power.

Memory intensive processes may suffer from memory bandwidth saturation [8, 14]. During the execution of such processes, if data cannot be moved from main memory to the cores fast enough, the cores may sit idle as they wait for the data to arrive. These processes may obtain limited benefit from increasing processor frequency due to the slow speed of cache and memory access relative to processor speed. Thus when executing a task containing both CPU intensive and memory intensive processes, it may be beneficial to move such memory intensive processes to lower frequency cores, while allowing less memory intensive, more CPU intensive processes to execute upon higher frequency cores.

The Linux 2.6 real time task scheduler minimizes response times for critical real-time tasks, while maximizing CPU utilization, by implementing dynamic task prioritization and task preemption [16]. That is, to prevent tasks from starving other tasks that need to use the CPU, the Linux 2.6 scheduler can dynamically alter a task's priority. A task's priority is dictated by its nice value, with a lower nice value indicating a higher priority. Also the Linux 2.6 scheduler allows preemption, meaning a lower priority task won't execute when a higher priority task is ready to run. By default, all processes have a nice value of 0, thus having the same priority. However, tasks may be assigned different priorities, based upon their nice values. This may affect the completion order of a group of concurrently executing tasks.

Context switching less CPU intensive processes, that would benefit less from executing upon higher frequency cores, to lower frequency cores and allowing CPU intensive processes to execute upon higher frequency cores may minimize performance loss while providing significant power savings. Doing so in a manner that does not affect process completion order as dictated by process priority is also beneficial. This research's goal is to identify

and quantify these advantages.

#### 1.1 Contributions

Like some recent work using heterogeneous processors [14, 5, 32, 2, 17, 30, 35, 20, 19, 21, 11, 33, 25, 26, 10, 13, 22], this research uses processors that have the same instruction architecture but have different implementation characteristics, such as operating frequency. In contrast to these works, however, our paper offers the following contributions.

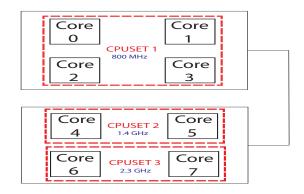

We present four CPU scheduling algorithms, referred to in this paper as Algorithm CPU Scheduler, Algorithm Priority CPU Scheduler, Algorithm Cache Miss Priority CPU Scheduler, and Algorithm Context Switch Priority CPU Scheduler that lower the global power budget in a heterogeneous multicore (or manycore) system while creating a minimal performance loss (and in some cases a performance gain) given a task containing a set of processes to be executed on this system. Also, for the three latter algorithms, process completion order, as dictated by process priority, is not affected. These algorithms utilize hardware partitions composed of heterogeneous cpusets. The cpusets contain varying numbers of cores. The cores are identical, with the exception that cores belonging to the same cpuset operate at the same frequency, and cores belonging to different cpusets operate at different frequencies. The algorithms can be executed upon a system using any multicore/manycore chip supporting CPU frequency scaling, which includes most of the widely available chips, including the Intel Nehalem and AMD Opteron chips, and uses no specialized hardware or software.

Algorithms CPU Scheduler, Priority CPU Scheduler, Cache Miss Priority CPU Scheduler, and Context Switch Priority CPU Scheduler use "application-driven" feedback, in which the executing application gives feedback (regarding its performance) to the operating system, at runtime, and the operating system, in turn, schedules the system's CPU hardware resources based upon this feedback. At runtime, an application evaluates its performance and sends this feedback to the operating system. If the application has an increased performance, relative to other executing processes in the task, the operating system context switches the application to a cpuset containing cores operating at a lower frequency, whereas if an application has decreased performance, relative to other executing

Figure 1: General Overview of Algorithms 1 - 4

processes in the task, the operating system context switches the application to a cpuset containing cores operating at a higher frequency, in hopes of speeding up the execution of the application and thus lowering the average completion time of all processes in the task. In addition, the latter three algorithms use process priority (Linux nice values), both static and dynamic, as a scheduling criterion and do not affect process completion order in a scenario where each process is assigned a distinct nice value. Also, algorithms Cache Miss Priority CPU Scheduler and Context Switch Priority CPU Scheduler use the cache miss/cache reference ratio and the number of context switches and CPU migrations, respectively, as scheduling criteria with the goal of improving performance. A general overview of our algorithms is depicted in Figure 1.

Power reduction is achieved by utilizing the heterogeneous cpusets, many of which contain cores operating at a lower frequency than would be achieved if the same cores were executing the same processes using the "on demand" CPU frequency scaling governor, which is the default governor in a Linux based system. This results in significant power savings.

#### 1.2 Outline of the Dissertation

We start with a discussion of the design of multicore processors in Chapter 2. This includes an overview of the concept of multicore processors. We then discuss the events leading to the development of multicore processors. We also present an overview of the

architecture of multicore processors. Finally, we explain the concepts of homogeneous versus heterogeneous multicore processors. In Chapter 3, we discuss challenges associated with the implementation of multicore processors. We include a discussion of cache coherence, power and temperature management, and performance issues arising from the implementation of multicore processors. In Chapter 4 we state the motivation of this research, describe some results in related areas, and introduce our four CPU scheduling problems. The main contribution of this dissertation is presented in Chapters 5, 6, 7, and 8 where we present our solutions to the four problems, including descriptions of the variables and constants used in the algorithms, descriptions of the algorithms themselves, and formal presentations of our algorithms. The first algorithm, Algorithm CPU Scheduler, is presented in Chapter 5, the second, Algorithm *Priority CPU Scheduler*, is presented in Chapter 6, the third, Algorithm Cache Miss Priority CPU Scheduler, is presented in Chapter 7, and the fourth, Algorithm Context Switch Priority CPU Scheduler, is presented in Chapter 8. A discussion of the complexity of the algorithms, evaluation results, and other properties are included in Chapter 9. Finally, we conclude and present some ideas for future research in Chapter 10.

#### CHAPTER 2

#### MULTICORE PROCESSORS

#### 2.1 Overview

A multicore processor is an integrated circuit or single computing component upon which two or more independent processors (cores) have been attached for enhanced performance, reduced power consumption, and parallel processing. A multicore processor is comparable to having two or more separate processors installed on the same computer. However, because these processors are plugged into the same socket, the connection between them is faster.

The cores are units that read and execute CPU instructions such as add, move data, and branch. The multiple cores can execute multiple instructions simultaneously, thus increasing the overall speed of programs that can take advantage of parallel computing. These cores are typically integrated onto a single integrated circuit die, known as a chip multiprocessor (CMP), or onto multiple dies in a single chip package [23]. AMD, ARM, Broadcom, Intel, and VIA are among the companies that have produced or are currently working on multicore products.

A dual core processor has two cores (e.g. AMD Phenom II X2), a quad core processor has four cores (Intel i3, i5, i7), a hexa core processor contains six cores (AMD Phenom II X6), and an octa core processor contains eight cores (AMD Opteron 6134). Chips with tens or even hundreds of cores are the growing trend in processor development. Such chips are termed "manycore" chips. In a manycore processor, the number of cores is large enough such that traditional multi-processor techniques are not efficient, primarily due to issues with congestion in supplying instructions and data to all of the cores. In this case, network on chip technology is advantageous.

The cores in a multicore device can be coupled tightly or loosely by designers. One example is that cores may or may not share caches, and may utilize message passing or shared memory for inter-core communication. Common network topologies interconnecting cores include bus, ring, two-dimensional mesh, and crossbar. Also, as in single-processor systems, cores in a multicore system may utilize architectures such as superscalar, VLIW, vector processing, SIMD, or multithreading.

### 2.2 Development

Because single core processors are quickly reaching the physical limits of feasible complexity and speed, multicore processing is becoming a growing industry trend [29]. While various methods have been used to improve CPU performance, including instruction level parallelism (ILP) methods such as superscalar pipelining, many of these methods are inefficient for applications that contain code that is hard to predict. These applications can benefit more from thread level parallelism (TLP) methods. Multiple independent CPUs are commonly used to increase a system's overall TLP. Thus one contributing factor that led to the development of multicore processors is the demand for increased TLP.

The speedup of a program using a multicore processor in parallel computing is quantified using Amdahl's law. Amdahl's law states that the overall speedup of a program is

$$S = \frac{1}{(1-P) + \frac{P}{n}}$$

where P is the portion of the program that can be executed in parallel and n is the number of concurrent processors.

It was possible for decades to improve the performance of a CPU by shrinking the area of the integrated circuit. Also, for the same circuit area, more transistors could be utilized in the design, which increased functionality. Clock rates also increased in the late 20<sup>th</sup> century, from several megahertz in the 1980's to several gigahertz in the early 2000's. However, as the rate of speeding up processor frequency had slowed and reached a plateau, increased use of parallel computing in the form of multicore processors has been pursued to improve overall processing performance. Adding additional processor cores to the same chip should both

Figure 2: Basic Microprocessor Design

improve performance and dissipate less heat, "without the need to run at ruinous clock rates [18]". Thus both increased available space (due to improved manufacturing processes) and the demand for increased thread level parallelism have led to the development of multicore CPUs.

Today, multicore processors are used in a wide variety of applications, including general purpose, embedded, network, digital signal processing (DSP), and graphics.

Figure 3: Shared Memory Model (left) and Distributed Memory Model (right)

Figure 4: Block Diagrams of the Core 2 Duo and Athlon 64 X2 multicore processors

#### 2.3 Overview of Architecture

A basic overview of multicore architecture is as follows. The basic design of a microprocessor is depicted in Figure 2. Level 1 (L1) cache is very fast memory that is used to store data frequently used by a processor. It is also physically closest to a processor. Level 2 (L2) cache is just off-chip, is larger than L1 cache, and is slower than L1 cache, but is still much faster than main memory. It is used for the same purpose as L1 cache. Most systems have approximately 32 Kb of L1 cache and 2 Mb of L2 cache.

Communication between cores, and to main memory, is usually accomplished by using either a single communication bus or and interconnection network. A bus is used with a shared memory model and an interconnection network is used with a distributed memory model. A bus has limited scalability and leads to diminished performance after the number

Figure 5: Block Diagram of AMD Opteron 6100 processor

of cores is approximately thirty-two cores. Figure 3 depicts both the shared memory and distributed memory models.

Two examples of different multicore architectures are the Intel Core 2 Duo chip and the Advanced Micro Device's Athlon 64 X2 chip. Both architectures differ greatly. Figure 4 shows the architecture of both chips [27].

The Core 2 Duo uses a shared memory model with private L1 caches and a shared L2 cache, whereas the Athlon utilizes a distributed memory model with discrete L2 caches for each core. These L2 caches share a system request interface, and in doing so, eliminate the need for a bus. Figure 5 shows a block diagram of the AMD Opteron 6100 processor, which also uses per core L2 caches and is the processor used in this research. The Core 2 Duo, instead, uses a bus interface. It also has explicit thermal and power control units on chip.

#### 2.4 Homogeneous versus Heterogeneous Multicore Processors

Homogeneous multicore systems are systems with identical cores and use one core design that is repeated consistently. A heterogeneous multicore processor is one which uses a combination of different cores, each of which can be optimized for a different role. One area of heterogeneity can be a core's operating frequency.

A single-ISA heterogeneous multicore processor, or simply heterogeneous multicore processor, can consist of cores exposing the same instruction set architecture, but delivering different performance. The cores can differ in clock frequency and power consumption. Asymmetry (or heterogeneity) can be built in by design [20, 21], or may exist due to explicit clock frequency scaling [31]. The latter is the basis of the heterogeneity in our heterogeneous multicore multiprocessor system.

#### CHAPTER 3

## MULTICORE PROCESSOR

#### IMPLEMENTATION CHALLENGES

There are numerous challenges that arise with the implementation of a multicore processor system. Three of these, which will be discussed in this chapter, are cache coherence, power and heat dissipation, and performance.

#### 3.1 Cache Coherence

Cache coherence can be an issue with multicore processors because of distributed L1 and L2 caches. The copy of the data in a core's cache may not always be the most up-to-date version since each core has its own cache. An example of this may be a dual-core processor where each core brought a block of memory into its private cache. If one core writes a value to a specific location, when the second core tries to read that value from its cache, it won't have the updated copy unless its cache entry is invalidated and a cache miss occurs. This cache miss causes the second core's cache entry to be updated. Without this type of cache coherence policy, garbage data would be read and invalid results would be produced.

Generally, there are two schemes for cache coherence, a directory-based protocol and a snooping protocol. The directory-based protocol can be used on an arbitrary network, and therefore is scalable to many processors or cores. In this scheme, a directory is used that holds information about which memory locations are being shared in multiple caches and which are exclusively used by one core's cache. This directory knows when a block needs to be invalidated or updated. In contrast, the snooping protocol only works with a bus-based system, and uses a number of states to decide whether it needs to update cache entries and if it has control over writing to a block. Also, the snooping protocol is not scalable [12].

Figure 6: Relationship Between Core Operating Frequency and Power Consumption

Two different schemes of cache coherence are exemplified by Intel's Core 2 Duo and AMD's Athlon 64 X2 multicore chips. Intel's Core 2 Duo speeds up cache coherence by querying the second core's L1 cache and the shared L2 cache simultaneously. An extra benefit of a shared L2 cache is that a coherence protocol doesn't need to be set for this level. AMD's Athlon 64 X2 monitors cache coherence in both L1 and L2 caches. This method has more overhead than Intel's model, despite its attempt to speed this process up using the HyperTransport connection.

This overhead associated with cache coherence can degrade the performance of a multicore processor system. Also, if a process is context switched too often, it will also have a tendency to generate many cache misses since it changes the CPU upon which it executes frequently and may not find valid data in its new core's cache. As a result, a performance loss will also occur, due to the need for cache coherence and the need to fetch valid data from another core's cache. Thus a different strategy may need to be implemented if a process generates many cache misses during an algorithm's implementation.

#### 3.2 Power and Temperature Management

The design and implementation of today's multicore/manycore chips must consider power and heat dissipation as important issues. In theory, if two cores are placed on a single chip, without any further modification, the chip would consume twice as much power [27]. This increased power consumption creates an associated increase in heat dissipation. As mentioned earlier, thermal constraints also make the integration and design of a multicore chip difficult. This necessitates a method of power reduction and temperature management for a multicore chip upon which numerous power consuming cores are found.

One method to account for the large amount of heat produced by a multicore/manycore chip is to run the multiple cores at a lower frequency to reduce power consumption. Figure 6 shows the linear relationship between a core's operating frequency and its power consumption. One technique to lower a core's frequency is dynamic voltage and frequency scaling, or DVFS. By using this technique, the operating voltage and frequency of a processor can be decreased. DVFS is used to decrease the voltage and frequency of a processor in order to conserve power, particularly in laptops or other mobile devices [9]. With this decrease in power consumption comes a concomitant decrease in heat production. Due to the quadratic relation between the energy consumption and operating voltage and linear relation between the energy consumption and operating voltage and linear relation between the energy consumption and operating frequency of a microprocessor, the DVFS technique has been proven to be a highly effective method of achieving low power consumption for a CPU while maintaining performance requirements [6].

CPU underclocking is another technique in which a CPU can be set to run at a lower clock rate than it was specified to operate at to reduce a computer's power consumption and heat emission [34]. This technique can provide increased system stability in high heat environments. An example is a Pentium 4 processor clocked at 2.4 GHz that can be "underclocked" to 1.8 GHz and can then be run with reduced fan speeds. In fact, in laptops the processor is usually underclocked automatically when the computer is operating on batteries. Most recent notebook and desktop computers utilizing power-saving schemes, like AMD's PowerNow and Cooln'Quiet, underclock themselves automatically under a light processing load when the system BIOS and operating system support it [3].

Yet another power management technique for multicore chips is to incorporate a power management unit that has the authority to shut down unused cores or limit the amount of power to these cores. Also, some processors, like the Intel Core 2 Duo Notebook processor, can turn off parts of the CPU, which are not used, to save energy [15].

Two of the techniques mentioned in this section, DVFS and underclocking, scale a CPU's frequency. The algorithms presented in this paper also rely upon CPU frequency scaling to achieve power savings.

#### 3.3 Multicore Performance

Multicore chips can contribute to increased performance of a processor, but this benefit can only exist if parallelism is exploited. Multicore chips improve an operating system's ability to multitask applications. In other words, multiple tasks can run in parallel upon the cores of a multicore chip, thereby improving overall performance.

A related topic is multithreading, or other parallel processing technique to get the optimum performance from a multicore processor. "With the possible exception of Java, there are no widely used commercial development languages with [multithreaded] extensions." [7] Programmers often have to completely rework and rebuild applications to make them multithreaded. They have to write applications with subroutines able to be run upon different cores. This means that data dependencies have to be resolved or accounted for such as race conditions, communication latencies, or cache coherence. Also, multithreaded applications must be balanced, meaning one core should not be used much more than another, in order to take full advantage of multithreading in a multicore system.

However, through the use of parallel programming and multithreading, these challenges in multicore performance can often be overcome. Also, in an architecture composed of a heterogeneous multicore processor, each application and thread can execute upon a core that best suites its architectural properties, thus overcoming another multicore performance challenge. An architecture composed of a heterogeneous multicore processor may contain cores specialized for certain tasks. For example, threads conducting CPU intensive work may execute upon high frequency cores, while threads that are not CPU intensive may execute upon low frequency cores. In this manner, threads that can benefit the most from executing upon higher frequency cores, may do so, while non-CPU intensive threads can execute upon lower frequency cores. Examples of non-CPU intensive threads or applications are those executing many system calls or interrupts, those that are I/O bound, and memory intensive processes.

Finally, the last challenge with multicore performance can be overcoming the performance loss associated with context switching overhead. In a multicore/manycore processor, an application can often be context switched upon the cores of a multicore processor. These context switches and CPU migrations are associated with a context switching overhead. This overhead can occur from the actual migration of a process's state from one core to another, or the delay associated with cache (memory) access and cache coherence. If a process is context switched too often, it will have a tendency to generate many cache misses, since it is changing the CPU upon which it executes frequently, and each CPU or core often has its own L1 or L2 cache.

To overcome this challenge, Algorithms 3 and 4 presented in this paper, consider the cache miss/cache reference ratio and the number of context switches and CPU migrations as scheduling criteria. Thus, if a certain threshold for these criteria is reached, indicating that an executing process is undergoing a performance loss due to an increase of cache misses, context switches, or CPU migrations, then a different strategy is implemented. These strategies will be described in the next few chapters.

#### CHAPTER 4

# POWER/ENERGY CPU SCHEDULING PROBLEM FOR HETEROGENEOUS MULTICORE PROCESSOR

#### SYSTEMS

After extensively researching power concerns in the implementation of heterogeneous multiprocessor systems, we designed four algorithms concerned with lowering the global power budget in a heterogeneous multicore processor system while creating a minimal performance loss, and, in some cases, a performance gain. We state the motivation of this research in the next section. We state how other problems mentioned in earlier chapters are related to the problem solved in this chapter. Finally, we give both an informal explanation and formal statement of the problems to be solved.

The main results of this dissertation research are reported in the next four chapters. In Chapters 5, 6, 7, and 8 four CPU scheduling algorithms (Algorithm 1: CPU Scheduler, Algorithm 2: Priority CPU Scheduler, Algorithm 3: Cache Miss Priority CPU Scheduler, and Algorithm 4: Context Switch Priority CPU Scheduler), each with a different approach to lowering the global power budget of a heterogeneous multicore processor system, are presented. In each of these four chapters, we include a description of the variables and constants used in our algorithm, a detailed informal description of the algorithm itself, and a formal presentation of our algorithm. Evaluation results and other properties of all four algorithms are given in Chapter 9.

#### 4.1 Motivation

A novel approach to allocating CPU resources with the goal of lowering the global power budget and creating a minimal performance loss (or a performance gain) in a heterogeneous multicore processor system is to use "application-driven" feedback, in which an executing application gives feedback (regarding its performance) to the operating system at runtime, and the operating system, in turn, dynamically schedules the system's CPU hardware resources based upon this feedback. There are four approaches presented in this dissertation that are concerned with meeting this goal.

In the first approach, each process in the system has the same default Linux nice value of 0, and thus the same default priority. This approach does not use process priority as a variable. In the second approach, each process in the system has different (not necessarily unique) priorities. These priorities will be implemented using Linux nice values, and may or may not be the default nice value of 0. In addition, they may be static or dynamic. Also, if a process's priority is static, different trial types will be used in which a process will be assigned both high and low priorities. This approach uses a process's nice value as a variable. In the third approach, in addition to each process having dynamic priorities, the cache miss/reference ratio of a process at runtime is used as a scheduling factor. Finally, in the fourth approach, each process has a dynamic priority and the number of context switches and CPU migrations generated by the process at runtime is used as a scheduling factor.

Our approaches will utilize hardware partitions composed of heterogeneous cpusets. The cpusets will contain varying numbers of cores. The cores will be identical, with the exception that cores belonging to the same cpuset will operate at the same frequency, and cores belonging to different cpusets will operate at different frequencies.

Power savings will be achieved by utilizing the heterogeneous cpusets, many of which will contain cores operating at a lower frequency than would be achieved if the same cores were executing the same processes using the "on demand" CPU frequency scaling governor, which is the default governor in a Linux based system.

To compensate for the lack of parallelism available in cpusets containing fewer cores, the cpusets will have different numbers of CPU's, with the number of CPU's in a cpuset being inversely proportional to the frequency of its cores.

Application performance will be improved due to two main factors. Firstly, if an application has an increased performance, relative to the other executing processes in a task, the

operating system will context switch the application to a cpuset containing cores operating at a lower frequency, whereas if an application has decreased performance, relative to other executing processes in the task, the operating system will context switch the application to a cpuset containing cores operating at a higher frequency, in hopes of speeding up the execution of the application and thus lowering the average completion time of all processes in the task. Secondly, by context switching processes between cpusets, the algorithm will move memory intensive processes that may suffer form memory bandwidth saturation to lower frequency cores, while allowing less memory intensive, more CPU intensive processes to execute upon higher frequency cores. In addition, to lower context switching overhead without stifling the CPU migrations necessary to improve performance, the cache miss/reference ratio and the number of context switches and CPU migrations created by a running process will be used as scheduling criteria.

The objective of this research is to implement the approaches mentioned earlier to schedule the system's CPU resources, and, in the scenario where processes are assigned static or dynamic priorities that are not default priorities, to do so without creating a large context switching overhead nor adversely impacting process completion order as dictated by process priority.

#### 4.2 Related Work

The work by Ghiasi, Keller, and Rawson [14] seems the closest to our own. The authors used a task-to-frequency scheduler that placed tasks in a multiprocessor system consisting of heterogeneous processors, each running at fixed but differing frequencies. However, their scheme risked an initial performance loss, especially in a system with many active tasks. They used an initialization phase that used insertion sort to place tasks in ready queues. This leads to a worst case scenario when all tasks are originally allocated to the fastest frequency. In contrast, our algorithm uses a "throughput estimate" that considers the number of processes in a core's ready queue, thus avoiding a situation in which most, if not all, processes are assigned to the same core.

Also, the authors in [14] used mechanisms for throttling the pipeline, or fetch throttling,

to mimic the effects of frequency scaling. In contrast, our method uses kernel-directed frequency scaling to directly frequency scale cores. This is a much more direct, accurate, and effective means to scale and measure the frequencies of individual cores, and is not an approximation to frequency scaling. Our work also tests a wider range of core frequencies than [14]. In addition, we tested a task with eight concurrently executing processes, with each process having different execution characteristics. The authors in [14] did not perform a detailed analysis of a loaded system. Also, the effects, on performance, of how processors are paired were not examined.

In [35], Vajda presented a frequency scaling based scheduling algorithm. The algorithm allocated each core to only one application, however, and adjusted the frequency of the scalable cores, instead of using fixed frequency cores. This algorithm requires the operating system to actively re-calculate power budgets every time an application requests frequency boosting, which can result in performance loss. Also, unlike our work, the author relied on a simulator to evaluate his algorithm, rather than direct evaluation of his technique on real hardware.

Kumar, et al., [20] used a heterogeneity conscious thread-to-core assignment to demonstrate power savings. However, they also relied upon a simulator to measure their experimental results and to roughly model their cores. Also, there were minor differences in the instruction set architecture between the processors they modeled, since each processor was of a different generation. In contrast, our algorithm was executed upon a real multicore chip with identical cores, only differing in operating frequency. In addition, the authors assumed a maximum of one thread running at a time on only one core, and did not perform an analysis of a multithreaded application.

In another study [19], the same authors modeled a different set of cores to investigate processor power dissipation. However, again they used a simulator to model a diverse set of cores, rather than using real hardware. They also assumed that unused cores were completely powered down, rather than left idle, which is typically not the case in a real multicore system. Also, the authors constrained their problem to a single application switching among cores, and did not consider multiple threads on a single die.

Fedorova, Vengerov, and Doucette [11] presented a thread scheduler that attempts to

balance core assignment with the goal of reducing completion time jitter and inconsistent priority enforcement while targeting optimal performance. However, this scheduler can generate increased context-switching overhead when attempting to allocate each thread's execution time evenly across all system's cores. Their algorithm is based upon reinforcement learning that allows each system core to learn a benefit function that approximates the future instruction rate on that core. This benefit function is then used to make core assignment decisions. In contrast, the algorithm presented in this paper uses feedback in which an application gives runtime information concerning both its instructions per cycle (IPC) and fraction wait time (time spent in ready and wait queues) to the operating system, which then uses this information to make scheduling decisions.

Almeida, et al., [2] used the difference between the desired and obtained throughput of a system to scale up or down the frequency of a processor. They repeated the process until the obtained throughput gradually became closer to the desired throughput. They used frequency scaling, in contrast to our method, which uses cores of different fixed frequencies. However, the default CPU frequency scaling policy found in most Linux based systems can also scale CPUs' frequencies, offering a similar, if not better, advantage than the method presented in [2]. Also, the algorithm presented by these authors only considers a system's throughput, and not an application's runtime IPC, which can be crucial in making scheduling decisions.

Isci, et al., [17] presented a global power manager that attempted to meet a specific global power budget by adjusting the power modes of individual cores. They assigned one of three power modes to each core, Turbo, Efficient1, and Efficient2. However, in contrast to our work, the authors used a simulator to evaluate their work, rather than real hardware. Also, they assumed a per-core DVFS (dynamic voltage and frequency scaling) knob to be available to their global power manager, unlike our work, which uses identical cores operating at different but fixed frequencies.

In [1] the authors proposed an algorithm in which all tasks were also assigned static priorities. In their model, tasks were assigned permanently to processors (partitioned scheduling) and were assigned rate-monotonic priorities that were inversely proportional to their periods. They measured the efficiency of their algorithm in terms of both total energy consumption and feasibility. They proved that this problem is NP-Hard in the strong sense on  $m \geq 2$  processors, even when feasibility is guaranteed *a priori*. However, unlike our algorithm, they used DVS (dynamic voltage scaling) to scale the frequency of their CPUs and used a simulator to measure their results.

Similar to our work, Schonherr, et al., [28] also proposed an approach that uses differing process priorities. In their approach, they assigned background (unimportant) processes a lower priority (nice value) than foreground (important) processes. They used a "separation in time" technique, in which foreground processes were allowed to complete before processor frequency was reduced, after which background processes were then allowed to execute. However, their approach only creates a power savings in some test cases, and not all test cases, as ours does. Also, they measured how much energy the execution of their load needed above idle consumption and not total energy consumption. Unlike our approach, their approach assumed that a priori knowledge, about the behavior and characteristics of running tasks, was available and was not determined at runtime.

#### 4.3 Problem Specification

The goal of this research can be defined by four problem statements.

**Specification 4.3.1** (Problem 1). Given a set S of processes  $P_i$  in a given task T to be executed by a heterogeneous multicore/manycore processor system  $M_i$ , with all  $P'_i$ 's having identical priorities (the default Linux nice value of 0), schedule each  $P_i$  to execute upon the CPU(s) in  $M_i$  such that the global power budget of  $M_i$  is minimized, yet the performance gain of all  $P'_i$ 's executing upon  $M_i$  is maximized, and the performance loss of all  $P'_i$ 's executing upon  $M_i$  is minimized.

**Specification 4.3.2** (Problem 2). Given a set S of processes  $P_i$  in a given task T to be executed by a heterogeneous multicore/manycore processor system  $M_i$ , with each  $P_i$  having different static or dynamic (not necessarily unique) priorities, nice<sub>i</sub> (that may or may not

be the default Linux nice value of 0), schedule each  $P_i$  to execute upon the CPU(s) in  $M_i$  such that the global power budget of  $M_i$  is minimized, yet the performance gain of all  $P'_i$ s executing upon  $M_i$  is maximized, and the performance loss of all  $P'_i$ s executing upon  $M_i$  is minimized.

Specification 4.3.3 (Problem 3). Given a set S of processes  $P_i$  in a given task T to be executed by a heterogeneous multicore/manycore processor system  $M_i$ , with each  $P_i$  having different static or dynamic (not necessarily unique) priorities, nice<sub>i</sub> (that may or may not be the default Linux nice value of 0), schedule each  $P_i$  to execute upon the CPU(s) in  $M_i$ , while utilizing the cache miss/reference ratio of  $P_i$  at runtime as a scheduling factor, such that the global power budget of  $M_i$  is minimized, yet the performance gain of all  $P'_i$ 's executing upon  $M_i$  is maximized, and the performance loss of all  $P'_i$ 's executing upon  $M_i$  is minimized.

**Specification 4.3.4** (Problem 4). Given a set S of processes  $P_i$  in a given task T to be executed by a heterogeneous multicore/manycore processor system  $M_i$ , with each  $P_i$  having different static or dynamic (not necessarily unique) priorities, nice<sub>i</sub> (that may or may not be the default Linux nice value of 0), schedule each  $P_i$  to execute upon the CPU(s) in  $M_i$ , while utilizing the number of context switches and CPU migrations created by  $P_i$  at runtime as a scheduling factor, such that the global power budget of  $M_i$  is minimized, yet the performance gain of all  $P'_i$ s executing upon  $M_i$  is maximized, and the performance loss of all  $P'_i$ s executing upon  $M_i$  is minimized.

#### CHAPTER 5

#### ALGORITHM 1

#### Algorithm CPU Scheduler

In this section we present an application-driven feedback mediated CPU scheduling algorithm, referred to as Algorithm *CPU Scheduler*. The algorithm does not use process priority as a variable.

5.1 Variables and Constants Used in Algorithm CPU Scheduler. Algorithm CPU Scheduler uses the following variables and constants:

$P_i$ :: a single or multithreaded process; T:: a task comprised of one or more processes ( $P_i$ ) to be scheduled and executed by a multicore or manycore chip;  $num\_cpus$ :: number of CPUs (cores) on multicore or manycore chip;  $core_i$ :: a single core (CPU) on a multicore or manycore chip;  $cpuset_i$ :: a Linux cpuset, comprised of one or more homogeneous core;'s, all operating at the same frequency; however,  $core_i$  and  $core_j$  from a separate cpuset; or  $cpuset_j$  may operate at different frequencies;  $core\_freq_i$ :: operating frequency of any  $core_i$  in  $cpuset_i$  (MHz);  $ready\_queue_i$ :: ready queue of any core in  $cpuset_i$ ;  $avg\_ready\_queue\_threads_i$ :: average number of threads in  $ready\_queue_i$ ;  $throughput\_estimate\_a_i$ :: estimate of the throughput of  $cpuset_i$ ; if ( $avg\_ready\_queue\_threads_i \ge 1$ )  $throughput\_estimate\_a_i$

$= avg\_ready\_queue\_threads_i * (1 / core\_freq_i);$

else

```

throughput\_estimate\_a_i = 1 / core\_freq_i;

throughput\_estimate\_b_i :: estimate\ of\ the\ inverse\ of\ throughput\ of\ cpuset_i;

if (avg\_ready\_queue\_threads_i \ge 1)

throughput\_estimate\_b_i

= avg\_ready\_queue\_threads_i * core\_freq_i;

else

throughput\_estimate\_b_i = 1 / core\_freq_i;

num\_threads_i :: number of threads in process P_i;

IPC_i:: instructions per cycle for process P_i;

IPC_i = \sum_{j=0}^{num\_threads_i} IPC_j / num\_threads_i,

where j is a thread in P_i;

system\_time_i :: time \ spent \ by \ P_i \ while \ executing \ at \ the \ system \ level \ (kernel);

user\_time_i :: time \ spent \ by \ P_i \ while \ executing \ at \ the \ user \ level \ (application);

real\_time_i :: system\_time_i + user\_time_i;

fraction\_wait\_time_i :: fraction of total execution time spent by process <math>P_i,

waiting in the ready queues and I/O queues;

fraction\_wait\_time_i

=\textstyle\sum_{j=0}^{num\_threads_i} \left((real\_time_j - (system\_time_j + user\_time_j))/real\_time_j\right)

/ num\_threads_i,

where j is a thread in P_i;

performance\_index_i :: a Boolean value calculated for an executing process P_i

from IPC_i \ and \ fraction\_wait\_time_i;

performance\_index_i = true\ iff\ IPC_i < 1.7\ and\ fraction\_wait\_time_i > 0.5;

CPU\_intensity_i :: measure of the CPU intensity of process P_i; average CPU

utilization of all cores upon which P_i is executing

load_average :: average system load over a period of time; number of processes

using or waiting for all CPUs (all core_i's);

```

### 5.2 Description of Algorithm CPU Scheduler.

A description of the algorithm is as follows:

1. Processes are assigned to the ready queues of CPUs in a cpuset using a "throughput estimate" defined by the following two equations:

If (avg. # of threads in ready queues of a cpuset  $\geq 1$ )

- (a) throughput\_estimate\_a = avg. # of threads in that cpuset's ready queues \* ( 1 / frequency of any core in that cpuset )

- (b)  $throughput\_estimate\_b = avg. \# of threads in that cpuset's ready queues * frequency of any core in that cpuset$

(In case of a tie, assign process to cpuset with least average number of threads in ready queues.)

Else

- (a)  $throughput\_estimate\_a = 1$  / frequency of any core in that cpuset

- (b)  $throughput\_estimate\_b = 1$  / frequency of any core in that cpuset

Note: In Linux, there is no direct measurement of the number of processes in the ready queue of a single core (CPU) on a multicore chip. However, if processes are allocated to certain cpusets, an estimate of the average number of threads in the ready queue of a particular cpuset's core can be obtained by calculating ((run queue size of all ready queues combined / number of CPUs where CPU utilization = 100%) x average CPU utilization of CPU in that cpuset).

2. All newly-arriving processes are assigned to the cpuset with the least value of throughput\_estimate\_a<sub>i</sub>. (If possible, all newly-arriving processes are assigned to the cpusets with CPUs operating at higher frequencies and with fewer processes in their ready queues).

- 3. As a process  $P_i$  executes, a "performance index" is calculated from the IPC (instructions per cycle) and fraction wait time of  $P_i$ . This calculation is made asynchronously with respect to other concurrently executing processes.

- 4. If  $IPC_i$  is lower than a threshold (< 1.7), or  $fraction\_wait\_time_i$  is higher than a threshold (> 0.5), then the performance index for that process,  $performance\_index_i$  is evaluated as true. (The performance index of a process is evaluated as true if the process has decreased performance, caused by a decrease in its instructions per cycle rate, or due to longer periods of time spent by the process in the ready or wait queues. We chose an IPC threshold of 1.7 based upon process performance data indicating that these processes had an IPC value greater than 1.7 during initial phases of execution. We chose a fraction wait time threshold of 0.5 because it is the average of 0, which signifies that a process is not spending any time waiting in the ready and I/O queues, and 1, which signifies that a process is spending all of its execution time waiting in the ready and I/O queues).

- 5. At regular time intervals, for an executing process,  $performance\_index_i$  is calculated. Each interval is equal to approximately one-fifth of the process's total execution time.

- (a) If the process is CPU intensive (the average CPU utilization of all cores upon which it is executing is > 50%) and if the performance index is true for that process, throughput\_estimate\_a\_i is recalculated for all cpusets, and the process is context switched to the cpuset with the lowest value of throughput\_estimate\_a\_i. (A cpuset with a lower value of throughput\_estimate\_a\_i will contain CPUs operating at higher frequencies and fewer processes in the ready queues of its cores. The goal of context switching a CPU intensive process that has decreased performance to such a cpuset is to speed up the execution of that process. We chose a CPU utilization threshold of 50% to categorize a process as CPU intensive because we found, in our experiments, that the non-CPU intensive benchmarks used for our test cases all had a CPU utilization less than 50%, and the CPU intensive benchmarks that we tested all had a CPU utilization greater than

50%).

- (b) To account for performance saturation caused by memory access, if a process is <u>not</u> CPU intensive and if the load average is > num\_cpus, then the process is context switched to the cpuset with the lowest value of throughput\_estimate\_b<sub>i</sub>. (If the system is heavily loaded and the process is not CPU intensive, the process is context switched to a cpuset with lower frequency cores). If the load average is < num\_cpus and if the performance index is true, then this process is context switched to the cpuset with the lowest value of throughput\_estimate\_a<sub>i</sub>. (If the system is not heavily loaded, and the process has decreased performance, then the process is context-switched to a cpuset with higher frequency cores).

- 6. For a non-executing process, if the fraction wait time of that process,

fraction\_wait\_time\_i, is equal to 1, then throughput\_estimate\_a\_i is recalculated for all cpusets, and the process is assigned to the cpuset with the lowest value of throughput\_estimate\_a\_i. (If the process is waiting in the ready queues for the cores of a cpuset for too long, it is context switched to a cpuset with fewer processes in its ready queues).

- 7. At regular time intervals, the average number of threads in the ready queues of all cpusets is computed. If the average number of threads in the ready queues of any cpuset is less than 1, then a process is assigned to that cpuset. If two or more cpusets have an average number of threads in their ready queues that is less than 1, a process is first assigned to the cpuset with CPUs operating at the highest frequency. The process(s) chosen to migrate to the new cpuset are chosen in order of CPU intensity, with higher CPU intensive processes having higher priority. (If there is a cpuset containing a core with an empty ready queue, then a process is assigned to this core).

- 8. Thread parallelism is accounted for by the number and frequency of CPUs in cpusets (hardware), with the lack of parallelism available in cpusets with fewer CPUs compensated for by the higher frequencies of its CPUs.

- 9. The measure of the algorithm's effectiveness is:

- (a) Average Instructions Per Second / Watts

- =  $(\sum_{i=0}^{m} (Instructions Executed by P_i / Execution Time (seconds) for P_i) / m) / watts,$

where m = number of processes in task T

- (b) Average time required for all processes in task T to complete execution \* watts

- =  $(\sum_{i=0}^{m} Execution Time (seconds) for P_i / m) * watts,$ where m = number of processes in Task T

(A potentially more efficient algorithm will have a higher value of (a) and a lower value of (b))

## $Algorithm \ 1: Feedback - driven \ CPU \ Scheduling \ Algorithm$ $(CPU \ Scheduler)$

```

Start with a set S of processes P_i in a given task T:

for all P_i in T (concurrently){

//initially schedule a process

calculate\ throughput\_estimate\_a_i\ for\ all\ cpusets;

assign P_i to cpuset with least value of throughput_estimate_a_i;

//if non - executing process is in wait queue too long, context switch process

if(fraction\_wait\_time_i == 1){

recalculate throughput_estimate_a_i for all cpusets and assign P_i to cpuset

with least value of throughput_estimate_a_i;

}

do{}

execute P_i;

calculate CPU_intensity<sub>i</sub> for P_i;

calculate IPC_i and fraction\_wait\_time_i for P_i;